# 2.7-V TO 5.5-V, LOW POWER, 12-BIT, DIGITAL-TO-ANALOG CONVERTER WITH INTERNAL REFERENCE AND POWER DOWN

# **FEATURES**

- 12-Bit Voltage Output DAC

- Programmable Internal Reference

- Programmable Settling Time:

- 1 µs in Fast Mode

- 3.5 µs in Slow Mode

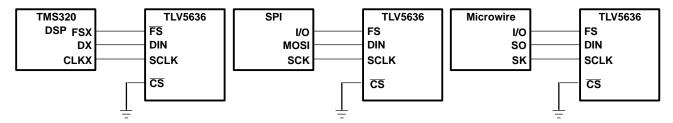

- Compatible With TMS320 and SPI<sup>™</sup> Serial Ports

- Differential Nonlinearity . . . < 0.5 LSB Typ

- Monotonic Over Temperature

# **APPLICATIONS**

- Digital Servo Control Loops

- Digital Offset and Gain Adjustment

- Industrial Process Control

- Machine and Motion Control Devices

- Mass Storage Devices

# **DESCRIPTION**

The TLV5636 is a 12-bit voltage output DAC with a flexible 4-wire serial interface. The serial interface allows glueless interface to TMS320 and SPI™, QSPI™, and Microwire™ serial ports. It is programmed with a 16-bit serial string containing 4 control and 12 data bits.

The resistor string output voltage is buffered by a x2 gain rail-to-rail output buffer. The programmable settling time of the DAC allows the designer to optimize speed vs power dissipation. With its on-chip programmable precision voltage reference, the TLV5636 simplifies overall system design.

Because of its ability to source up to 1 mA, the reference can also be used as a system reference. Implemented with a CMOS process, the device is designed for single supply operation from 2.7 V to 5.5 V. It is available in an 8-pin SOIC and 8-pin MSOP package to reduce board space in standard commercial and industrial temperature ranges

# **AVAILABLE OPTIONS**

| т -           | PACKAGE   |             |  |  |  |  |  |

|---------------|-----------|-------------|--|--|--|--|--|

| 'A            | SOIC (D)  | MSOP (DGK)  |  |  |  |  |  |

| 0°C to 70°C   | TLV5636CD | TLV5636CDGK |  |  |  |  |  |

| -40°C to 85°C | TLV5636ID | TLV5636IDGK |  |  |  |  |  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI, QSPI are trademarks of Motorola, Inc..

Microwire is a trademark of National Semiconductor Corporation.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

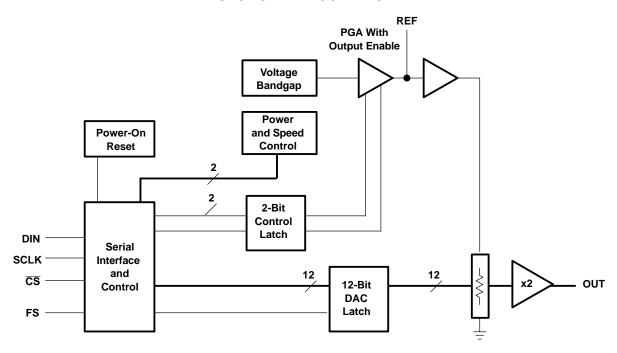

# **FUNCTIONAL BLOCK DIAGRAM**

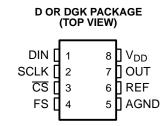

# **Terminal Functions**

|           | TERMINAL | I/O/P | DESCRIPTION                                                          |  |  |  |

|-----------|----------|-------|----------------------------------------------------------------------|--|--|--|

| NAME      | NO.      | 1/0/F | DESCRIPTION                                                          |  |  |  |

| AGND      | 5        | Р     | Ground                                                               |  |  |  |

| <u>cs</u> | 3        | I     | Chip select. Digital input active low, used to enable/disable inputs |  |  |  |

| DIN       | 1        | I     | Digital serial data input                                            |  |  |  |

| FS        | 4        | I     | Frame sync input                                                     |  |  |  |

| OUT       | 7        | 0     | DAC A analog voltage output                                          |  |  |  |

| REF       | 6        | I/O   | Analog reference voltage input/output                                |  |  |  |

| SCLK      | 2        | I     | Digital serial clock input                                           |  |  |  |

| $V_{DD}$  | 8        | Р     | Positive power supply                                                |  |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                                                      |          | UNIT                               |  |  |

|------------------------------------------------------|----------|------------------------------------|--|--|

| Supply voltage (V <sub>DD</sub> to AGND)             |          | 7 V                                |  |  |

| Reference input voltage                              |          | - 0.3 V to V <sub>DD</sub> + 0.3 V |  |  |

| Digital input voltage range                          |          | - 0.3 V to V <sub>DD</sub> + 0.3 V |  |  |

| Operating free air temperature range. T              | TLV5636C | 0°C to 70°C                        |  |  |

| Operating free-air temperature range, T <sub>A</sub> | TLV5636I | -40°C to 85°C                      |  |  |

| Storage temperature range, T <sub>stg</sub>          |          | -65°C to 150°C                     |  |  |

| Lead temperature 1,6 mm (1/16 inch) from case for 1  | 260°C    |                                    |  |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

|                                                     |                          | MIN  | NOM   | MAX                   | UNIT |

|-----------------------------------------------------|--------------------------|------|-------|-----------------------|------|

| Cumply valtage V                                    | V <sub>DD</sub> = 5 V    | 4.5  | 5     | 5.5                   | V    |

| Supply voltage, V <sub>DD</sub>                     | $V_{DD} = 3 V$           | 2.7  | 3     | 3.3                   | V    |

| Power on Reset, POR                                 | 0.55                     |      | 2     | V                     |      |

| High level digital input valtage V                  | DV <sub>DD</sub> = 2.7 V | 2    |       |                       |      |

| High-level digital input voltage, V <sub>IH</sub>   | DV <sub>DD</sub> = 5.5 V | 2.4  |       |                       | V    |

| Law law digital input waltage V                     | DV <sub>DD</sub> = 2.7 V |      |       | 0.6                   | V    |

| Low-level digital input voltage, V <sub>IL</sub>    | DV <sub>DD</sub> = 5.5 V |      |       | 1                     |      |

| Defended with the NEE terminal                      | $V_{DD} = 5 V^{(1)}$     | AGND | 2.048 | V <sub>DD</sub> - 1.5 | V    |

| Reference voltage, V <sub>ref</sub> to REF terminal | $V_{DD} = 3 V^{(1)}$     | AGND | 1.024 | V <sub>DD</sub> - 1.5 | V    |

| Load resistance, R <sub>L</sub>                     | ·                        | 2    |       |                       | kΩ   |

| Load capacitance, C <sub>L</sub>                    |                          |      |       | 100                   | pF   |

| Clock frequency, f <sub>CLK</sub>                   |                          |      |       | 20                    | MHz  |

| On another for a six to man another. T              | TLV5636C                 | 0    |       | 70                    | 00   |

| Operating free-air temperature, T <sub>A</sub>      | TLV5636I                 | -40  |       | 85                    | °C   |

<sup>(1)</sup> Due to the x2 output buffer, a reference input voltage . (V<sub>DD</sub> - 0.4 V)/2 causes clipping of the transfer function. The output buffer of the internal reference must be disabled, if an external reference is used.

# **ELECTRICAL CHARACTERISTICS**

over recommended operating free-air temperature range, supply voltages, and reference voltages (unless otherwise noted)

| POWER           | POWER SUPPLY                 |                                                   |                           |  |     |     |      |  |  |  |

|-----------------|------------------------------|---------------------------------------------------|---------------------------|--|-----|-----|------|--|--|--|

|                 | PARAMETER                    | TEST CON                                          | TEST CONDITIONS           |  |     | MAX | UNIT |  |  |  |

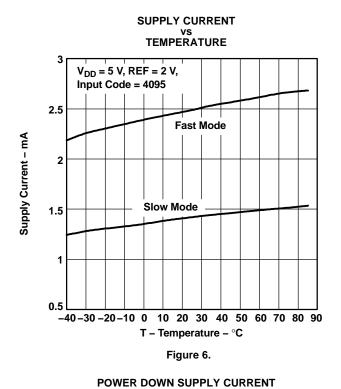

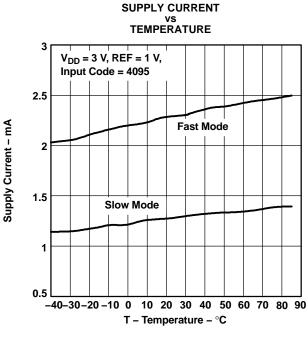

|                 |                              | No load,                                          | Fast                      |  | 2.3 | 3.3 |      |  |  |  |

| I <sub>DD</sub> | Power supply current         | All inputs = AGND or $V_{DD}$ , DAC latch = 0x800 | Slow                      |  | 1.5 | 1.9 | mA   |  |  |  |

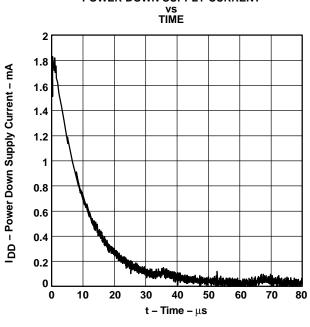

|                 | Power-down supply current    | See Figure 8                                      | See Figure 8              |  |     | 10  | μA   |  |  |  |

| DCDD            | Dower comply rejection retio | Zero scale (1)                                    | Zero scale <sup>(1)</sup> |  |     |     | dB   |  |  |  |

| PSRR            | Power supply rejection ratio | Full Scale (2)                                    | Full Scale (2)            |  |     |     | иь   |  |  |  |

<sup>(1)</sup> Power supply rejection ratio at zero scale is measured by varying  $V_{DD}$  and is given by: PSRR = 20 log [( $E_{ZS}(V_{DD}max) - E_{ZS}(V_{DD}min)$ )/ $V_{DD}max$ ]

<sup>(2)</sup> Power supply rejection ratio at full scale is measured by varying V<sub>DD</sub> and is given by: PSRR = 20 log [(E<sub>G</sub>(V<sub>DD</sub>max) - E<sub>G</sub>(V<sub>DD</sub>min))/V<sub>DD</sub>max]

# **ELECTRICAL CHARACTERISTICS**

over recommended operating free-air temperature range, supply voltages, and reference voltages (unless otherwise noted)

| STATIC             | STATIC DAC SPECIFICATIONS                     |                         |     |      |      |                 |  |  |  |  |

|--------------------|-----------------------------------------------|-------------------------|-----|------|------|-----------------|--|--|--|--|

|                    | PARAMETER                                     | TEST CONDITIONS         | MIN | TYP  | MAX  | UNIT            |  |  |  |  |

|                    | Resolution                                    |                         | 12  |      |      | Bits            |  |  |  |  |

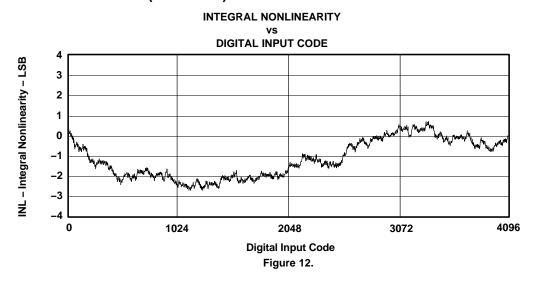

| INL                | Integral nonlinearity                         | See note <sup>(1)</sup> |     | ±2   | ±4   | LSB             |  |  |  |  |

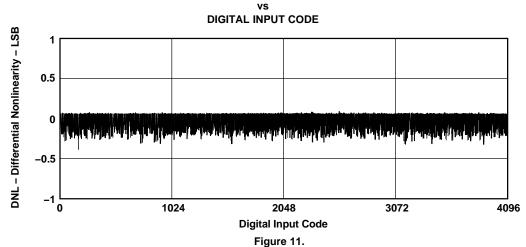

| DNL                | Differential nonlinearity                     | See note <sup>(2)</sup> |     | ±0.5 | ±1   | LSB             |  |  |  |  |

| E <sub>ZS</sub>    | Zero-scale error (offset error at zero scale) | See note <sup>(3)</sup> |     |      | ±20  | mV              |  |  |  |  |

| E <sub>ZS</sub> TC | Zero-scale-error temperature coefficient      | See note (4)            |     | 10   |      | μV/°C           |  |  |  |  |

| E <sub>G</sub>     | Gain error                                    | See note <sup>(5)</sup> |     |      | ±0.6 | % of FS voltage |  |  |  |  |

| E <sub>G</sub> TC  | Gain error temperature coefficient            | See note (6)            |     | 10   |      | ppm/°C          |  |  |  |  |

- (1) The relative accuracy or integral nonlinearity (INL) sometimes referred to as linearity error, is the maximum deviation of the output from the line between zero and full scale excluding the effects of zero code and full-scale errors. Tested from code 10 to code 4095.

- The differential nonlinearity (DNL) sometimes referred to as differential error, is the difference between the measured and ideal 1 LSB amplitude change of any two adjacent codes. Monotonic means the output voltage changes in the same direction (or remains constant) as a change in the digital input code. Tested from code 10 to code 4095.

- Zero-scale error is the deviation from zero voltage output when the digital input code is zero.

- Zero-scale-error temperature coefficient is given by:  $E_{ZS}$  TC =  $[E_{ZS}$  (T<sub>max</sub>)  $E_{ZS}$  (T<sub>min</sub>)]/V<sub>ref</sub> x 10<sup>6</sup>/(T<sub>max</sub> T<sub>min</sub>). Gain error is the deviation from the ideal output (2V<sub>ref</sub> 1 LSB) with an output load of 10 k $\Omega$  excluding the effects of the zero-error. Gain error temperature coefficient is given by:  $E_{C}$  TC =  $[E_{C}(T_{max}) E_{C}(T_{min})]/V_{ref}$  x 10<sup>6</sup>/(T<sub>max</sub> T<sub>min</sub>).

| (6) Gain error tempera          |                                     | $C = [E_G(I_{max}) - E_G(I_{min})]/V_{ref} \times C$  | · · · · · · · · · · · · · · · · · · · | n/·   |       |                       |                 |  |

|---------------------------------|-------------------------------------|-------------------------------------------------------|---------------------------------------|-------|-------|-----------------------|-----------------|--|

| P/                              | ARAMETER                            | TEST CONDITION                                        | S                                     | MIN   | TYP   | MAX                   | UNIT            |  |

| V <sub>O</sub> Voltag           | ge output range                     | $R_L = 10 \text{ k}\Omega$                            | $R_L = 10 \text{ k}\Omega$            |       |       |                       |                 |  |

| Outpu                           | it load regulation accuracy         | V <sub>O</sub> = 4.096 V, 2.048 V, R <sub>L</sub> = 2 | kΩ                                    |       |       | ±0.25                 | % of FS voltage |  |

| REFERENCE PIN CO                | NFIGURED AS OUTPUT (REF)            |                                                       |                                       |       |       |                       |                 |  |

| F                               | PARAMETER                           | TEST CONDITION                                        | IS                                    | MIN   | TYP   | MAX                   | UNIT            |  |

| V <sub>ref(OUTL)</sub> Low re   | eference voltage                    |                                                       |                                       | 1.003 | 1.024 | 1.045                 | V               |  |

|                                 | eference voltage                    | V <sub>DD</sub> > 4.75 V                              |                                       | 2.027 | 2.048 | 2.068                 | V               |  |

|                                 | t source current                    |                                                       |                                       |       |       | 1                     | mA              |  |

| I <sub>ref(sink)</sub> Outpu    | t sink current                      |                                                       |                                       | -1    |       |                       | mA              |  |

| Load                            | capacitance                         |                                                       |                                       |       |       | 100                   | pF              |  |

| PSRR Power                      | r supply rejection ratio            |                                                       |                                       |       | -65   |                       | dB              |  |

| REFERENCE INPUT                 | CONFIGURED AS INPUT (REF)           |                                                       |                                       |       |       |                       |                 |  |

| PARAM                           | ETER                                | TEST CONDITIONS                                       |                                       | MIN   | TYP   | MAX                   | UNIT            |  |

| V <sub>I</sub> Input voltage    |                                     |                                                       |                                       | O     | )     | V <sub>DD</sub> - 1.5 | V               |  |

| R <sub>i</sub> Input resistance | ce                                  |                                                       |                                       |       | 10    |                       | kΩ              |  |

| C <sub>i</sub> Input capacitai  | nce                                 |                                                       |                                       |       |       |                       | pF              |  |

| Poforonco inni                  | ut bandwidth PEE - 0.3              | 0.2 V <sub>DD</sub> + 1.024 V dc                      |                                       |       | 1.3   |                       | MHz             |  |

| Kelelelice liipi                | Reference input bandwidth REF = 0.2 |                                                       | pp + 1.024 V dc Slow                  |       |       |                       | IVII IZ         |  |

| Reference fee                   | d through REF = 1 \                 | <sub>o</sub> at 1 kHz + 1.024 V dc <sup>(1)</sup>     |                                       |       | -80   |                       | dB              |  |

(1) Reference feedthrough is measured at the DAC output with an input code = 0x000.

| DIGIT           | DIGITAL INPUT                    |                      |     |     |     |      |  |  |  |  |

|-----------------|----------------------------------|----------------------|-----|-----|-----|------|--|--|--|--|

|                 | PARAMETER                        | TEST CONDITIONS      | MIN | TYP | MAX | UNIT |  |  |  |  |

| I <sub>IH</sub> | High-level digital input current | $V_I = V_{DD}$       |     |     | 1   | μA   |  |  |  |  |

| I <sub>IL</sub> | Low-level digital input current  | V <sub>I</sub> = 0 V | -1  |     |     | μΑ   |  |  |  |  |

| Ci              | Input capacitance                |                      |     | 8   |     | pF   |  |  |  |  |

# **ELECTRICAL CHARACTERISTICS**

over recommended operating free-air temperature range, supply voltages, and reference voltages (unless otherwise noted)

| ANALOG (           | ANALOG OUTPUT DYNAMIC PERFORMANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |                              |      |     |     |      |      |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------|------|-----|-----|------|------|--|--|

|                    | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TES                                                                                | T CONDITIONS                 | MIN  | TYP | MAX | UNIT |      |  |  |

|                    | Output pottling time (full peole)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    | C <sub>L</sub> = 100 pF,     | Fast |     | 1   | 3    |      |  |  |

| t <sub>s(FS)</sub> | Output settling time (full scale)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $R_L = 10 \text{ k}\Omega,$<br>see note <sup>(1)</sup>                             | $C_L = 100 \text{ pr},$      | Slow |     | 3.5 | 7    | μs   |  |  |

|                    | A Control of the cont |                                                                                    | $C_1 = 100 \text{ pF},$      | Fast |     | 0.5 | 1.5  | ше   |  |  |

| t <sub>s(CC)</sub> | Output settling time, code to code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | see note(2)                                                                        | C <sub>L</sub> = 100 pr,     | Slow |     | 1   | 2    | μs   |  |  |

| SR                 | Slew rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $R_L = 10 \text{ k}\Omega$                                                         | C <sub>L</sub> = 100 pF,     | Fast |     | 8   |      | V/µs |  |  |

| SK .               | Siew rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | see note <sup>(3)</sup>                                                            |                              | Slow |     | 1.5 |      | v/µs |  |  |

|                    | Glitch energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\frac{\text{DIN} = 0 \text{ to } 1,}{\text{CS}} = V_{\text{DD}}$                  | $f_{out} = 1 \text{ kHz},$   |      |     | 5   |      | nV-s |  |  |

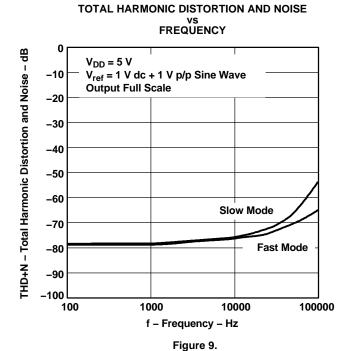

| SNR                | Signal-to-noise ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                    |                              |      | 71  | 75  |      |      |  |  |

| S/(N+D)            | Signal-to-noise + distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f <sub>s</sub> = 480 kSPS,                                                         | $f_{out} = 1 \text{ kHz},$   |      | 59  | 66  |      | dB   |  |  |

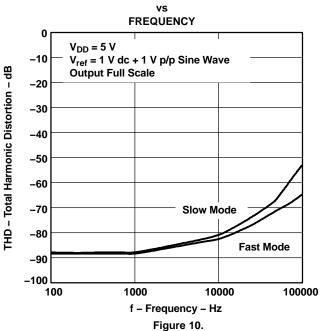

| THD                | Total harmonic distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $ \begin{cases} f_s = 480 \text{ kSPS}, \\ R_L = 10 \text{ k}\Omega, \end{cases} $ | $C_{L}^{m} = 100 \text{ pF}$ |      |     | -67 | -59  | ub   |  |  |

|                    | Spurious free dynamic range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                    |                              |      | 59  | 69  |      |      |  |  |

<sup>(1)</sup> Settling time is the time for the output signal to remain within +0.5 LSB of the final measured value for a digital input code change of 0x20 to 0xFDF and 0xFDF to 0x020 respectively. Assured by design; not tested.

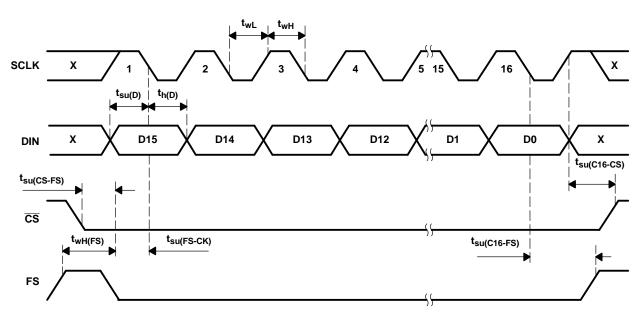

# **TIMING REQUIREMENTS**

| DIGITAL INPUTS          |                                                                                                                                                                                                                                                                                       |     |     |     |      |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|

|                         |                                                                                                                                                                                                                                                                                       | MIN | NOM | MAX | UNIT |  |  |  |

| t <sub>su(CS-FS)</sub>  | Setup time, CS low before FS falling edge                                                                                                                                                                                                                                             | 10  |     |     | ns   |  |  |  |

| t <sub>su(FS-CK)</sub>  | Setup time, FS low before first negative SCLK edge                                                                                                                                                                                                                                    | 8   |     |     | ns   |  |  |  |

| t <sub>su(C16-FS)</sub> | Setup time, 16 <sup>th</sup> negative edge after FS low on which bit D0 is sampled before rising edge of FS.                                                                                                                                                                          | 10  |     |     | ns   |  |  |  |

| t <sub>su(C16-CS)</sub> | Setup time, 16 <sup>th</sup> positive SCLK edge (first positive after D0 is sampled) before $\overline{\text{CS}}$ rising edge. If FS is used instead of 16 <sup>th</sup> positive edge to update DAC, then setup time between FS rising edge and $\overline{\text{CS}}$ rising edge. | 10  |     |     | ns   |  |  |  |

| t <sub>wH</sub>         | SCLK pulse duration high                                                                                                                                                                                                                                                              | 25  | -   |     | ns   |  |  |  |

| t <sub>wL</sub>         | SCLK pulse duration low                                                                                                                                                                                                                                                               | 25  |     |     | ns   |  |  |  |

| t <sub>su(D)</sub>      | Setup time, data ready before SCLK falling edge                                                                                                                                                                                                                                       | 8   | •   |     | ns   |  |  |  |

| t <sub>h(D)</sub>       | Hold time, data held valid after SCLK falling edge                                                                                                                                                                                                                                    | 5   | •   |     | ns   |  |  |  |

| t <sub>wH(FS)</sub>     | FS duration high                                                                                                                                                                                                                                                                      | 25  |     |     | ns   |  |  |  |

<sup>(2)</sup> Settling time is the time for the output signal to remain within +0.5 LSB of the final measured value for a digital input code change of one count. Assured by design; not tested.

<sup>(3)</sup> Slew rate determines the time it takes for a change of the DAC output from 10% to 90% full-scale voltage.

# PARAMETER MEASUREMENT INFORMATION

Figure 1. Timing Diagram

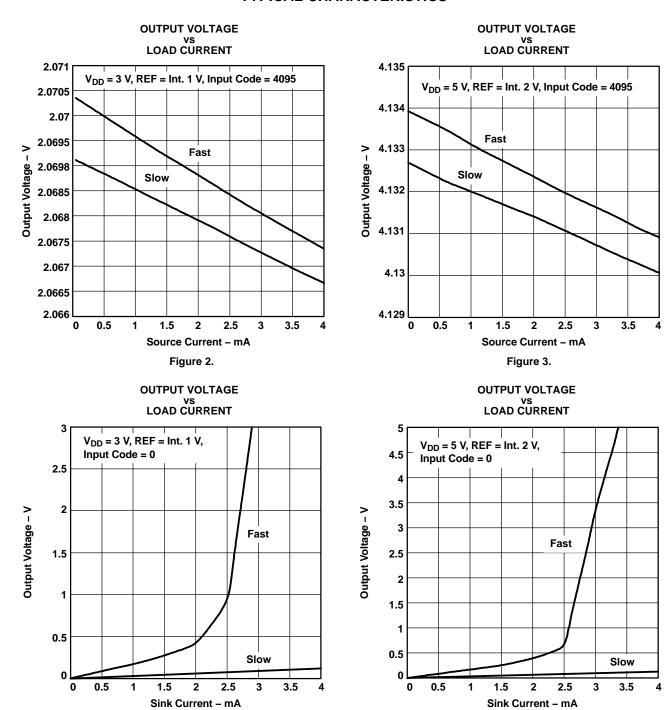

# **TYPICAL CHARACTERISTICS**

Figure 4.

Figure 5.

# **TYPICAL CHARACTERISTICS (continued)**

Figure 7.

Figure 8.

8

# **TYPICAL CHARACTERISTICS (continued)**

# DIFFERENTIAL NONLINEARITY

# **TYPICAL CHARACTERISTICS (continued)**

#### **APPLICATION INFORMATION**

#### **GENERAL FUNCTION**

The TLV5636 is a 12-bit, single supply DAC, based on a resistor string architecture. It consists of a serial interface, a speed and power-down control logic, a programmable internal reference, a resistor string, and a rail-to-rail output buffer.

The output voltage (full scale determined by external reference) for each channel is given by:

$$2 REF \frac{CODE}{2^n} [V]$$

where REF is the reference voltage and CODE is the digital input value within the range of  $0_{10}$  to  $2^{n-1}$ , where n = 12 (bits). The 16-bit data word, consisting of control bits and the new DAC value, is illustrated in the *data* format section. A power-on reset initially resets the internal latches to a defined state (all bits zero).

#### **SERIAL INTERFACE**

The device has to be enabled with  $\overline{CS}$  set to low. A falling edge of FS starts shifting the data bit-per-bit (starting with the MSB) to the internal register on high-low transitions of SCLK. After 16 bits have been transferred or FS rises, the content of the shift register is moved to the DAC latch, which updates the voltage output to the new level.

The serial interface of the TLV5636 can be used in two basic modes:

- Four wire (with chip select)

- Three wire (without chip select)

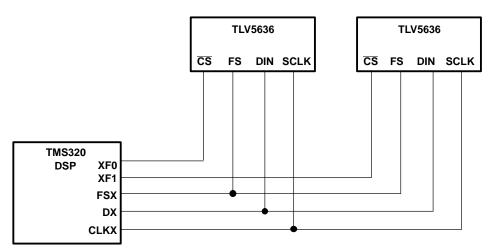

Using chip select (four-wire mode), it is possible to have more than one device connected to the serial port of the data source (DSP or microcontroller). Figure 13 shows an example with two TLV5636s connected directly to a TMS320 DSP.

Figure 13. TMS320 Interface

If there is no need to have more than one device on the serial bus, then  $\overline{\text{CS}}$  can be tied low. Figure 14 shows an example of how to connect the TLV5636 to TMS320, SPI<sup>TM</sup> or Microwire<sup>TM</sup> using only three pins.

# **APPLICATION INFORMATION (continued)**

Figure 14. Three Wire Interface

Notes on SPI and Microwire: Before the controller starts the data transfer, the software has to generate a falling edge on the I/O pin connected to FS. If the word width is 8 bits (SPI and Microwire), two write operations must be performed to program the TLV5636. After the write operation(s), the DAC output is updated automatically on the next positive clock edge following the sixteenth falling clock edge.

#### SERIAL CLOCK AND UPDATE RATE

The maximum serial clock frequency is given by:

$$f_{sclkmax} = \frac{1}{t_{whmin} + t_{wlmin}} = 20 \text{ MHz}$$

(1)

The maximum update rate is:

$$f_{\text{updatemax}} = \frac{1}{16 \left( t_{\text{whmin}} + t_{\text{wlmin}} \right)} = 1.25 \text{ MHz}$$

(2)

Note that the maximum update rate is just a theoretical value for the serial interface, as the settling time of the TLV5636 has to be considered, too.

#### **DATA FORMAT**

The 16-bit data word for the TLV5636 consists of two parts:

- Program bits (D15..D12)

- New data (D11..D0)

|   | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6    | D5      | D4 | D3 | D2 | D1 | D0 |

|---|-----|-----|-----|-----|-----|-----|----|----|----|-------|---------|----|----|----|----|----|

| ſ | R1  | SPD | PWR | R0  |     |     |    |    |    | 12 Da | ta bits |    |    |    |    |    |

SPD : Speed control bit 1 = fast mode 0 = slow mode

PWR : Power control bit 1 = power down 0 = normal operation

The following table lists the possible combination of the register select bits:

# **Register Select Bits**

| R1 | R0 | REGISTER                       |  |  |

|----|----|--------------------------------|--|--|

| 0  | 0  | Write data to DAC              |  |  |

| 0  | 1  | Reserved                       |  |  |

| 1  | 0  | Reserved                       |  |  |

| 1  | 1  | Write data to control register |  |  |

The meaning of the 12 data bits depends on the selected register. For the DAC register, the 12 data bits determine the new DAC output value:

**Data Bits: DAC**

| D11           | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---------------|-----|----|----|----|----|----|----|----|----|----|----|

| New DAC value |     |    |    |    |    |    |    |    |    |    |    |

If the control register is selected, then D1, D0 of the 12 data bits are used to program the reference voltage:

#### **Data Bits: CONTROL**

| D11              | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1   | D0   |

|------------------|-----|----|----|----|----|----|----|----|----|------|------|

| X <sup>(1)</sup> | Χ   | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | REF1 | REF2 |

<sup>(1)</sup> X = don't care

REF1 and REF0 determine the reference source. If internal reference is selected, REF1 and REF0 determine the reference voltage.

#### Reference Bits

| REF1 | REF0 | REFERENCE |

|------|------|-----------|

| 0    | 0    | External  |

| 0    | 1    | 1.024 V   |

| 1    | 0    | 2.048 V   |

| 1    | 1    | External  |

#### **CAUTION:**

If external reference voltage is applied to the REF pin, external reference MUST be selected.

# **EXAMPLE:**

Set DAC output, select fast mode, select internal reference at 2.048 V:

# Set reference voltage to 2.048 V (CONTROL register):

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 1   | 1   | 0   | 1   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

# Write new DAC value and update DAC output:

| 15 | D14 | D13 | D12 | D11                  | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|-----|-----|-----|----------------------|-----|----|----|----|----|----|----|----|----|----|----|

| 0  | 1   | 0   | 0   | New DAC output value |     |    |    |    |    |    |    |    |    |    |    |

The DAC output is updated on the rising clock edge after D0 is sampled.

To output data consecutively using the same DAC configuration, it is not necessary to program the CONTROL register again.

# LINEARITY, OFFSET, AND GAIN ERROR USING SINGLE END SUPPLIES

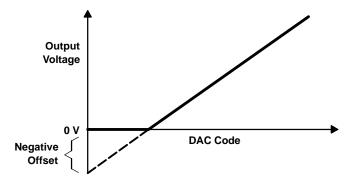

When an amplifier is operated from a single supply, the voltage offset can still be either positive or negative. With a positive offset, the output voltage changes on the first code change. With a negative offset, the output voltage may not change with the first code, depending on the magnitude of the offset voltage.

The output amplifier attempts to drive the output to a negative voltage. However, because the most negative supply rail is ground, the output cannot drive below ground and clamps the output at 0 V.

The output voltage then remains at zero until the input code value produces a sufficient positive output voltage to overcome the negative offset voltage, resulting in the transfer function shown in Figure 15.

Figure 15. Effect of Negative Offset (Single Supply)

This offset error, not the linearity error, produces this breakpoint. The transfer function would have followed the dotted line if the output buffer could drive below the ground rail.

For a DAC, linearity is measured between zero-input code (all inputs 0) and full-scale code (all inputs 1) after offset and full scale are adjusted out or accounted for in some way. However, single supply operation does not allow for adjustment when the offset is negative due to the breakpoint in the transfer function. So the linearity is measured between full-scale code and the lowest code that produces a positive output voltage.

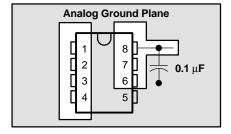

# POWER-SUPPLY BYPASSING AND GROUND MANAGEMENT

Printed-circuit boards that use separate analog and digital ground planes offer the best system performance. Wire-wrap boards do not perform well and should not be used. The two ground planes should be connected together at the low-impedance power-supply source. The best ground connection may be achieved by connecting the DAC AGND terminal to the system analog ground plane, making sure that analog ground currents are well managed and there are negligible voltage drops across the ground plane.

A 0.1- $\mu$ F ceramic-capacitor bypass should be connected between  $V_{DD}$  and AGND and mounted with short leads as close as possible to the device. Use of ferrite beads may further isolate the system analog supply from the digital power supply.

Figure 16 shows the ground plane layout and bypassing technique.

Figure 16. Power-Supply Bypassing

#### **DEFINITIONS OF SPECIFICATIONS AND TERMINOLOGY**

## Integral Nonlinearity (INL)

The relative accuracy or integral nonlinearity (INL), sometimes referred to as linearity error, is the maximum deviation of the output from the line between zero and full scale excluding the effects of zero code and full-scale errors.

#### **Differential Nonlinearity (DNL)**

The differential nonlinearity (DNL), sometimes referred to as differential error, is the difference between the measured and ideal 1 LSB amplitude change of any two adjacent codes. Monotonic means the output voltage changes in the same direction (or remains constant) as a change in the digital input code.

# Zero-Scale Error (E<sub>ZS</sub>)

Zero-scale error is defined as the deviation of the output from 0 V at a digital input value of 0.

#### Gain Error (E<sub>G</sub>)

Gain error is the error in slope of the DAC transfer function.

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms value of the first six harmonic components to the value of the fundamental signal. The value for THD is expressed in decibels.

#### Signal-To-Noise Ratio + Distortion (S/N+D)

S/N+D is the ratio of the rms value of the output signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for S/N+D is expressed in decibels.

### Spurious Free Dynamic Range (SFDR)

Spurious free dynamic range is the difference between the rms value of the output signal and the rms value of the largest spurious signal within a specified bandwidth. The value for SFDR is expressed in decibels.

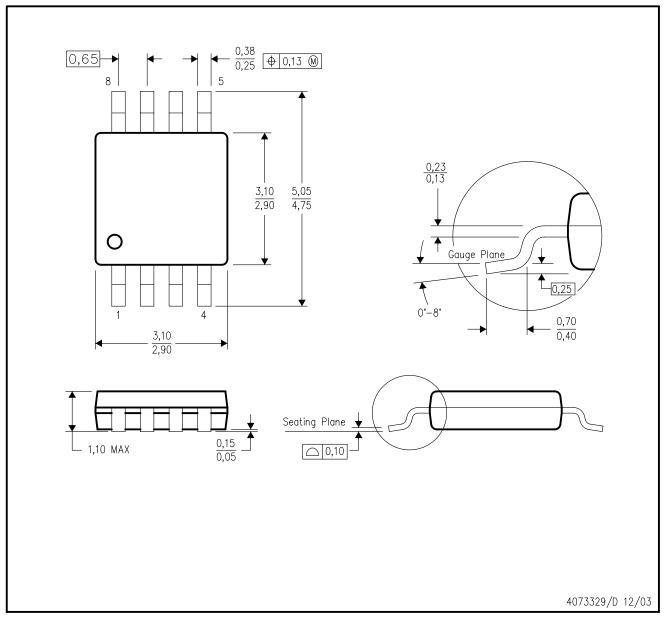

# DGK (S-PDSO-G8)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Falls within JEDEC MO-187 variation AA.

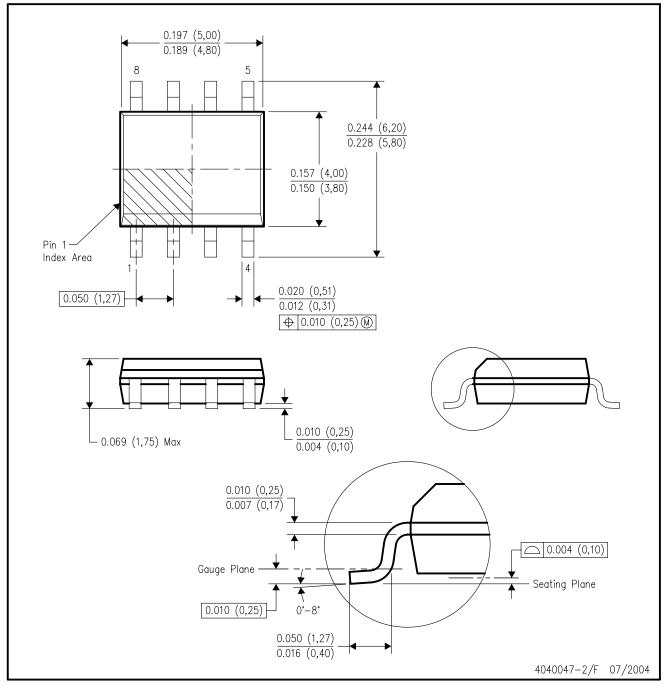

# D (R-PDSO-G8)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-012 variation AA.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated