# LM12434/LM12{L}438 12-Bit + Sign Data Acquisition System with Serial I/O and Self-Calibration

### **General Description**

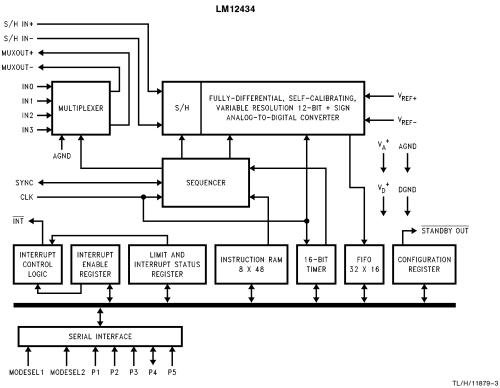

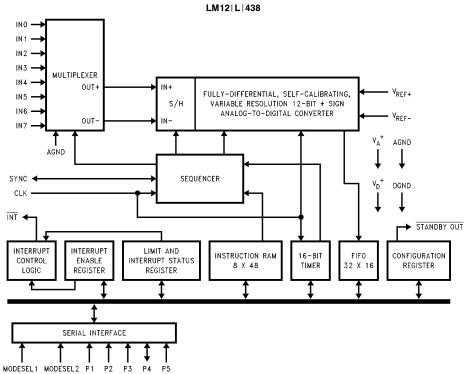

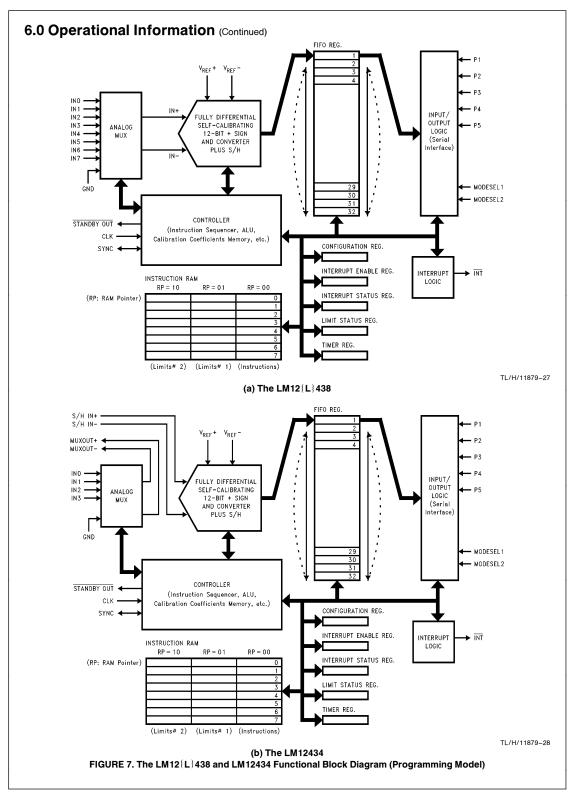

The LM12434 and LM12{L}438 are highly integrated Data Acquisition Systems. Operating on 3V to 5V, they combine a fully-differential self-calibrating (correcting linearity and zero errors) 13-bit (12-bit + sign) analog-to-digital converter (ADC) and sample-and-hold (S/H) with extensive analog and digital functionality. Up to 32 consecutive conversions, using two's complement format, can be stored in an internal 32-word (16-bit wide) FIFO data buffer. An internal 8-word instruction RAM can store the conversion sequence for up to eight acquisitions through the LM12{L}438's eight-input multiplexer. The LM12434 has a four-channel multiplexer, a differential multiplexer output, and a differential S/H input. The LM12434 and LM12{L}438 can also operate with 8-bit + sign resolution and in a supervisory "watchdog" mode that compares an input signal against two programmable

Acquisition times and conversion rates are programmable through the use of internal clock-driven timers. The differential reference voltage inputs can be externally driven for absolute or ratiometric operation.

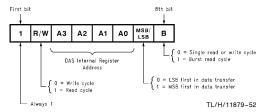

All registers, RAM, and FIFO are directly accessible through the high speed and flexible serial I/O interface bus. The serial interface bus is user selectable to interface with the following protocols with zero glue logic: MICROWIRE/ PLUSTM, Motorola's SPI/QSPI, Hitachi's SCI, 8051 Family's Serial Port (Mode 0), I2C and the TMS320 Family's Serial

An evaluation kit for demonstrating the LM12434 and LM12{L}438 is available.

TRI-STATE® is a registered trademark of National Semiconductor Corporation. MICROWIRE/PLUSTM is a trademark of National Semiconductor Corporation. Windows® is a registered trademark of Microsoft Corporation.

### **Key Specifications**

f<sub>CLK</sub> = 8 MHz {L, f<sub>CLK</sub> = 6 MHz} ■ Resolution 12-bi 12-bit + sign or 8-bit + sign ■ 13-bit conversion time 5.5  $\mu$ s {7.3  $\mu$ s} (max) ■ 9-bit conversion time 2.6  $\mu$ s {3.5  $\mu$ s} (max)

13-bit Through-put rate 140k samples/s {105k sample/s} (min)

Comparison time ("watchdog" mode)

1.4 µs {1.8 µs} (max) 10 MHz {6 MHz} (max) ■ Serial Clock ■ Integral Linearity Error ±1 LSB (max) V<sub>IN</sub> range GND to  $V_A^{\,+}$ Power dissipation 45 mW {20 mW} (max)

■ Stand-by mode

power dissipation 25 μW {16.5 μW} (tvp) ■ Supply voltage LM12L438  $3.3V\ \pm 10\%$ 5V ±10% LM12434/8

#### **Features**

- Three operating modes: 12-bit + sign, 8-bit + sign, and "watchdog" comparison mode

- Single-ended or differential inputs

- Built-in Sample-and-Hold

- Instruction RAM and event sequencer

- 8-channel (LM12{L}438) or 4-channel (LM12434) multiplexer

- 32-word conversion FIFO

- Programmable acquisition times and conversion rates

- Self-calibration and diagnostic mode

- Power down output for system power management

- Read while convert capability for maximum through-put

### **Applications**

- Data Logging

- Portable Instrumentation

- Process Control

- **Energy Management**

- Robotics

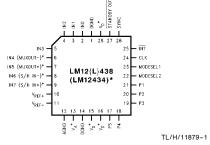

### **Connection Diagrams**

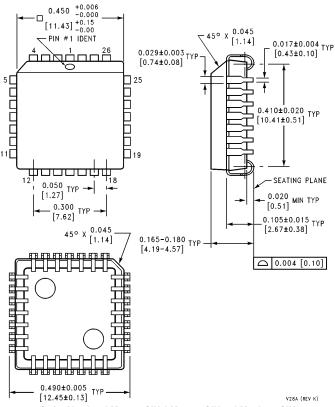

#### 28-Pin PLCC Package

\*Pin names in () apply to the LM12434

Order Number LM12434CIV, LM12438CIV, or LM12L438CIV See NS Package Number V28A

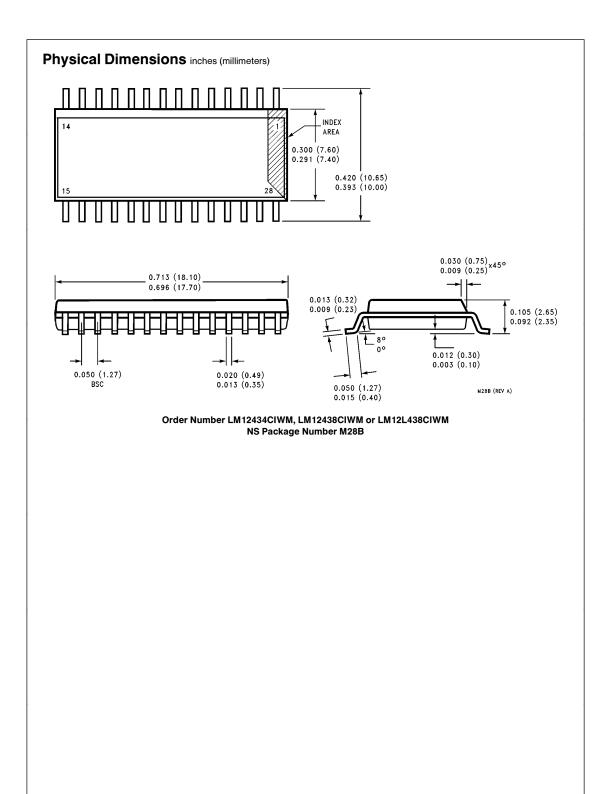

#### 28-Pin Wide Body SO Package

Order Number LM12434CIWM, LM12438CIWM, or

LM12L438CIWM See NS Package Number M28B

**Table of Contents**

| 1.0 FUNCTIONAL DIAGRAMS                                                                                                                   | 3  |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.0 ELECTRICAL SPECIFICATIONS                                                                                                             | 5  |

| 2.1 Ratings                                                                                                                               | 5  |

| 2.1.1 Absolute Maximum Ratings                                                                                                            | 5  |

| 2.1.2 Operating Ratings                                                                                                                   | 5  |

| 2.2 Performance Characteristics                                                                                                           | 5  |

| 2.2.1 Converter Static Characteristics                                                                                                    | 5  |

| 2.2.2 Converter Dynamic Characteristics                                                                                                   |    |

| 2.2.3 DC Characteristics                                                                                                                  |    |

| 2.2.4 Digital DC Characteristics                                                                                                          |    |

| 2.3 Digital Switching Characteristics                                                                                                     | 10 |

| 2.3.1 Standard Interface Mode                                                                                                             |    |

| 2.3.2 8051 Interface Mode                                                                                                                 |    |

| 2.3.3 TMS320 Interface Mode                                                                                                               |    |

| 2.3.4 I <sup>2</sup> C Bus Interface                                                                                                      | 13 |

| 2.4 Notes on Specifications                                                                                                               | 14 |

| 3.0 ELECTRICAL CHARACTERISTICS                                                                                                            | 15 |

| 4.0 TYPICAL PERFORMANCE CHARACTERISTICS .                                                                                                 | 19 |

| 5.0 PIN DESCRIPTIONS                                                                                                                      | 23 |

| 6.0 OPERATIONAL INFORMATION                                                                                                               | 27 |

| 6.1 Functional Description                                                                                                                | 27 |

| 6.2 Internal User-Accessible Registers                                                                                                    | 31 |

| COAL III DAM                                                                                                                              |    |

| 6.2.1 Instruction RAM                                                                                                                     | 31 |

| 6.2.2 Configuration Register                                                                                                              |    |

|                                                                                                                                           | 38 |

| 6.2.2 Configuration Register                                                                                                              | 38 |

| 6.2.2 Configuration Register                                                                                                              | 38 |

| 6.2.2 Configuration Register 6.2.3 Interrupts 6.2.4 Interrupt Enable Register 6.2.5 Interrupt Status Register 6.2.6 Limit Status Register | 38 |

| 6.2.2 Configuration Register 6.2.3 Interrupts 6.2.4 Interrupt Enable Register 6.2.5 Interrupt Status Register                             | 38 |

| 7.0 DIGITAL INTERFACE                                              | 43            |  |

|--------------------------------------------------------------------|---------------|--|

| 7.1 Standard Interface Mode                                        | 43            |  |

| 7.1.1 Examples of Interfacing to the H<br>MICROWIRE/PLUS™ and 68HC |               |  |

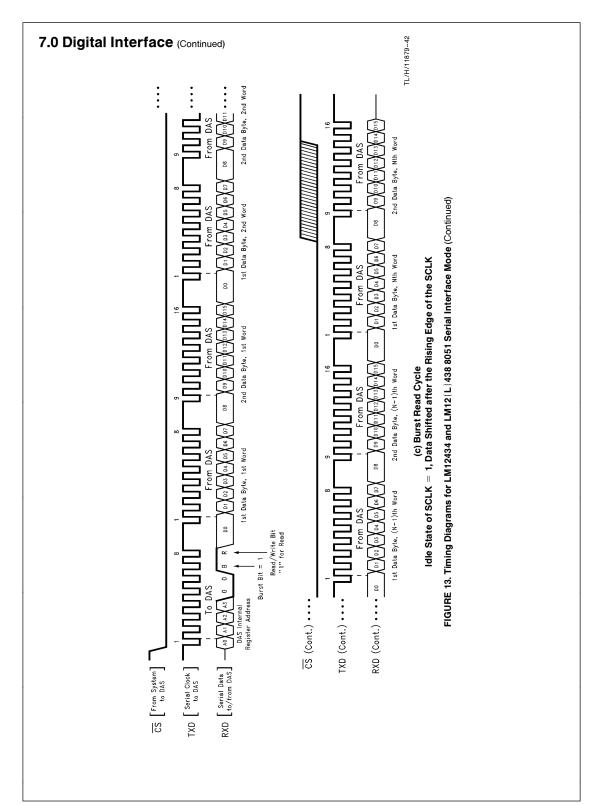

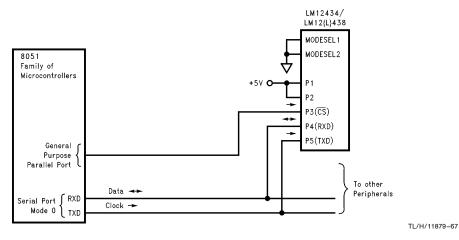

| 7.2 8051 Interface Mode                                            | 59            |  |

| 7.2.1 Example of Interfacing to the 805                            | 162           |  |

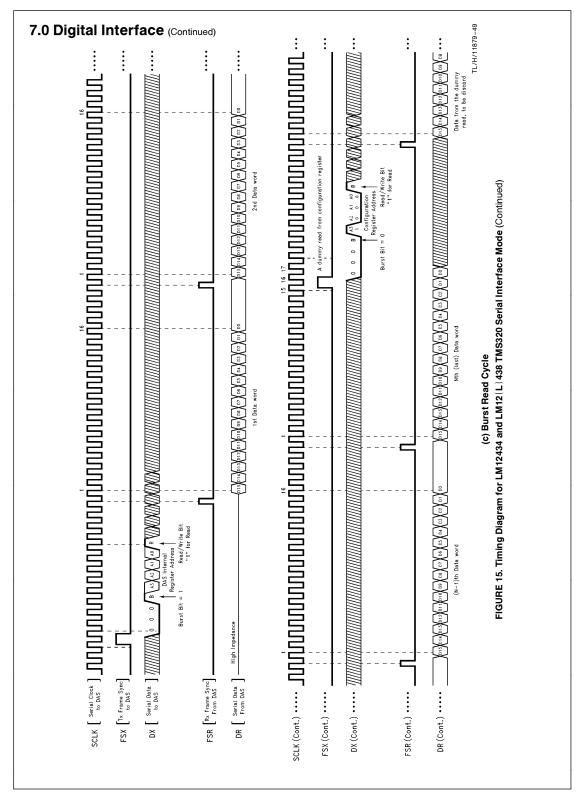

| 7.3 TMS320 Interface Mode                                          | 66            |  |

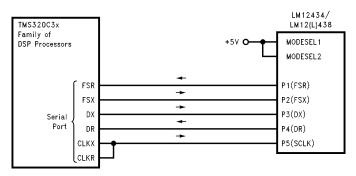

| 7.3.1 Example of Interfacing to the TMS                            | 3320C3x69     |  |

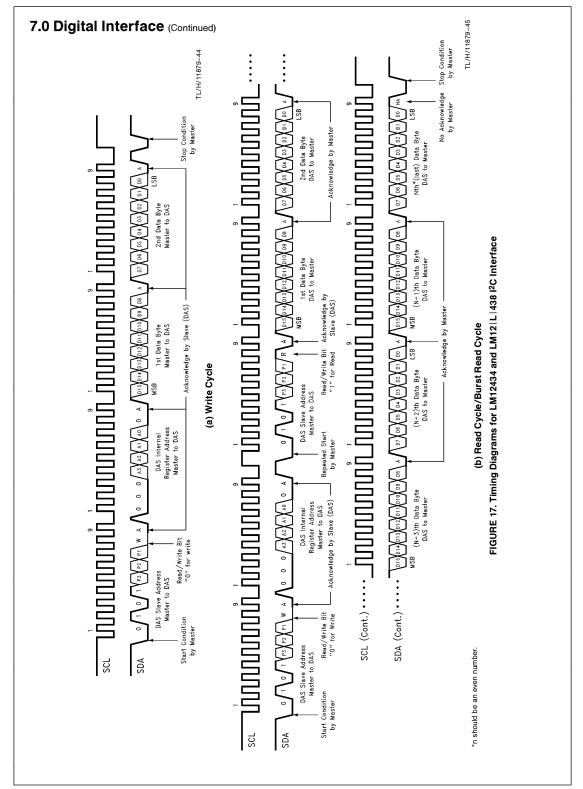

| 7.4 I <sup>2</sup> C Bus Interface                                 | 74            |  |

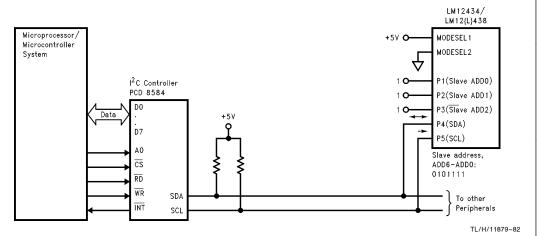

| 7.4.1 Example of Interfacing to an I <sup>2</sup> C C              | Controller 76 |  |

| 8.0 ANALOG CONSIDERATIONS                                          | 77            |  |

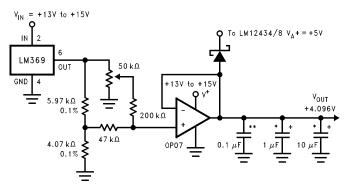

| 8.1 Reference Voltage                                              | 77            |  |

| 8.2 Input Range                                                    | 77            |  |

| 8.3 Input Current                                                  | 77            |  |

| 8.4 Input Source Resistance                                        | 77            |  |

| 8.5 Input Bypass Capacitance                                       | 77            |  |

| 8.6 Input Noise                                                    | 77            |  |

| 8.7 Power Supply Consideration                                     | 77            |  |

| 8.8 PC Board Layout and Grounding Consideration                    | deration78    |  |

# 1.0 Functional Diagrams

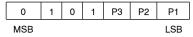

| INTERFACE        | MODESEL1 | MODESEL2 | P1   | P2   | P3            | P4  | P5   |

|------------------|----------|----------|------|------|---------------|-----|------|

| Standard         | 0        | 1        | R/F  | CS   | DI            | DO  | SCLK |

| 8051             | 0        | 0        | 1*   | 1*   | <del>CS</del> | RXD | TXD  |

| I <sup>2</sup> C | 1        | 0        | SAD0 | SAD1 | SAD2          | SDA | SCL  |

| TMS320           | 1        | 1        | FSR  | FSX  | DX            | DR  | SCLK |

<sup>\*</sup>Internal pull-up

# Ordering Information (LM12434)

| Part Number Package Type |                     | NSC Package Number | Temperature Range |

|--------------------------|---------------------|--------------------|-------------------|

| LM12434CIV               | 28-Pin PLCC         | V28A               | -40°C to +85°C    |

| LM12434CIWM              | 28-Pin Wide Body SO | M28B               | -40°C to +85°C    |

# 1.0 Functional Diagrams (Continued)

TL/H/11879-4

| INTERFACE        | MODESEL1 | MODESEL2 | P1   | P2        | P3   | P4  | P5   |

|------------------|----------|----------|------|-----------|------|-----|------|

| Standard         | 0        | 1        | R/F  | <u>cs</u> | DI   | DO  | SCLK |

| 8051             | 0        | 0        | 1*   | 1*        | CS   | RXD | TXD  |

| I <sup>2</sup> C | 1        | 0        | SAD0 | SAD1      | SAD2 | SDA | SCL  |

| TMS320           | 1        | 1        | FSR  | FSX       | DX   | DR  | SCLK |

<sup>\*</sup>Internal pull-up

# Ordering Information (LM12{L}438)

| Part Number                 | Package Type                                 | NSC Package Number | Temperature Range |  |  |  |

|-----------------------------|----------------------------------------------|--------------------|-------------------|--|--|--|

| LM12438CIV<br>LM12L438CIV   | 28-Pin PLCC                                  | V28A               | -40°C to +85°C    |  |  |  |

| LM12438CIWM<br>LM12L438CIWM | 28-Pin Wide Body SO                          | M28B               | -40°C to +85°C    |  |  |  |

| LM12438 Eval                | Evaluation Board and Windows® based software |                    |                   |  |  |  |

### 2.0 Electrical Specifications

#### 2.1 RATINGS

#### 2.1.1 Absolute Maximum Ratings (Notes 1 & 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage ( $V_A^+$  and  $V_D^+$ ) 6.0V

Voltage at Input and Output Pins

except IN0-IN3 (LM12434) -0.3 V to  $V^+ \, + \, 0.3 V$

and IN0-IN7 (LM12{L}438)

Voltage at Analog Inputs IN0-IN3 (LM12434)

$\widehat{\mathsf{GND}} - \widehat{\mathsf{5V}} \mathsf{to} \mathsf{V}^+ + \mathsf{5V}$ and IN0-IN7 (LM12(L)438)  $|V_A^+ - V_D^+|$ 300 mV

AGND - DGND 300 mV

Input Current at Any Pin (Note 3)  $\pm\,5\,\text{mA}$ Package Input Current (Note 3)  $\pm\,20~mA$

Power Dissipation (T<sub>A</sub> = 25°C) (Note 4)

V Package WM Package

Storage Temperature

$-65^{\circ}$ C to  $+150^{\circ}$ C

Soldering Information, Lead Temperature (Note 19)

V Package, Vapor Phase (60 seconds)

Infrared (15 seconds)

WM Package, Vapor Phase (60 seconds)

Infrared (15 seconds)

ESD Susceptibility (Note 5)

1.5 kV

#### 2.1.2 Operating Ratings (Notes 1 & 2)

Temperature Range  $(T_{min} \leq T_A \leq T_{max})$ LM12434CIV/LM12{L}438CIV  $-40^{\circ}C \leq T_{A} \leq 85^{\circ}C$ LM12434CIWM, LM12{L}438CIWM  $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$

Supply Voltage

$V_A^+, V_D^+$ 3.0V to 5.5V  $|V_A{}^+-V_D{}^+|$  $\leq$  100 mV AGDND - DGND  $\leq$  100 mV Analog Inputs Range  $\text{GND} \leq \text{V}_{IN+} \, \leq \, \text{V}_{A}^{\,+}$

V<sub>REF+</sub> Input Voltage  $1V \le V_{REF+} \le V_A^+$ V<sub>REF</sub> - Input Voltage  $0V \leq V_{REF-} \leq V_{REF+} - 1V$

$1V \leq V_{REF} \leq V_A^+$

V<sub>REF+</sub> - V<sub>REF-</sub> V<sub>REF</sub> Common Mode

Range (Note 16)  $0.1~V_A{}^+~\leq V_{REFCM} \leq 0.6~V_A{}^+$

- 2.2 PERFORMANCE CHARACTERISTICS All specifications apply to the LM12434, LM12438, and LM12L438 unless otherwise noted. Specifications in braces { } apply only to the LM12L438.

- 2.2.1 Converter Static Characteristics The following specifications apply to the LM12434 and LM12{L}438 for  $V_A{}^+$  $V_{D}^{+} = 5V (3.3V)$ , AGND = DGND = 0V,  $V_{REF+} = 4.096V (2.5V)$ ,  $V_{REF-} = 0V$ , 12-bit + sign conversion mode,  $f_{CLK} = 0$ 8.0 MHz  $\{6 \text{ MHz}\}$ ,  $R_S=25\Omega$ , source impedance for  $V_{REF+}$  and  $V_{REF-}\leq25\Omega$ , fully-differential input with fixed 2.048V {1.25V} common-mode voltage, and minimum acquisition time unless otherwise specified. Boldface limits apply for TA =  $T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ . (Notes 6, 7, 8 and 9)

| Symbol | Parameter                                                                             | Conditions                    | Typical<br>(Note 10) | Limits<br>(Note 11)   | Units<br>(Limit) |

|--------|---------------------------------------------------------------------------------------|-------------------------------|----------------------|-----------------------|------------------|

| ILE    | Positive and Negative Integral<br>Linearity Error                                     | After Auto-Cal (Notes 12, 17) | ± 0.35               | ± 1                   | LSB (max)        |

| TUE    | Total Unadjusted Error                                                                | After Auto-Cal (Note 12)      | ±1                   |                       | LSB              |

|        | Resolution with No Missing Codes                                                      | After Auto-Cal (Note 12)      |                      | 13                    | Bits             |

| DNL    | Differential Non-Linearity                                                            | After Auto-Cal                | ±0.2                 | ± 1                   | LSB (max)        |

|        | Zero Error                                                                            | After Auto-Cal (Notes 13, 17) | ±0.2                 | ± 1                   | LSB (max)        |

|        | Positive Full-Scale Error                                                             | After Auto-Cal (Notes 12, 17) | ±0.2                 | ± 2                   | LSB (max)        |

|        | Negative Full-Scale Error                                                             | After Auto-Cal (Notes 12, 17) | ±0.2                 | ± 2                   | LSB (max)        |

|        | DC Common Mode Error                                                                  | (Note 14)                     | ±2                   | ± <b>3.5</b> { ± 4.0} | LSB (max)        |

| ILE    | 8-Bit + Sign and "Watchdog"<br>Mode Positive and Negative<br>Integral Linearity Error | (Note 12)                     | ±0.15                | ± 1/2                 | LSB (max)        |

| TUE    | 8-Bit + Sign and "Watchdog" Mode<br>Total Unadjusted Error                            | After Auto-Zero               | ±1/2                 | ± 1/2                 | LSB (max)        |

|        | 8-Bit + Sign and "Watchdog" Mode<br>Resolution with No Missing Codes                  |                               |                      | 9                     | Bits (max)       |

**2.2.1 Converter Static Characteristics** The following specifications apply to the LM12434 and LM12{L}438 for  $V_A{}^+=V_D{}^+=5V$  {3.3V}, AGND = DGND = 0V,  $V_{REF+}=4.096V$  {2.5V},  $V_{REF-}=0$ V, 12-bit + sign conversion mode,  $f_{CLK}=8.0$  MHz {6 MHz},  $R_S=25\Omega$ , source impedance for  $V_{REF+}$  and  $V_{REF-}\leq25\Omega$ , fully-differential input with fixed 2.048V {1.25V} common-mode voltage, and minimum acquisition time unless otherwise specified. **Boldface limits apply for T\_A = T\_J = T\_{MIN} to T\_{MAX}**; all other limits  $T_A = T_J = 25^{\circ}C$ . (Notes 6, 7, 8 and 9) (Continued)

| Symbol                                    |                                          | Parameter                                | Conditions                                                            | Typical<br>(Note 10)   | Limits<br>(Note 11)                   | Units<br>(Limit)              |

|-------------------------------------------|------------------------------------------|------------------------------------------|-----------------------------------------------------------------------|------------------------|---------------------------------------|-------------------------------|

| DNL                                       | 8-Bit + Sign an<br>Differential Non      | d "Watchdog" Mode<br>-Linearity          |                                                                       | ±0.15                  | ± 1/2                                 | LSB (max)                     |

|                                           | 8-Bit + Sign an<br>Zero Error            | d "Watchdog" Mode                        | After Auto-Zero                                                       | ±0.05                  | ± 1/2                                 | LSB (max)                     |

|                                           | 8-Bit + Sign an and Negative F           | d "Watchdog" Positive<br>ull-Scale Error |                                                                       | ±0.1                   | ± 1/2                                 | LSB (max)                     |

|                                           | 8-Bit + Sign an DC Common M              | d "Watchdog" Mode<br>ode Error           |                                                                       | ±1/8                   |                                       | LSB                           |

|                                           | Multiplexer Cha<br>Matching              | nnel-to-Channel                          |                                                                       | ±0.05                  |                                       | LSB                           |

| V <sub>IN+</sub>                          | Non-Inverting Input Range                |                                          |                                                                       |                        | GND<br>V <sub>A</sub> +               | V (min)<br>V (max)            |

| V <sub>IN</sub> -                         | Inverting<br>Input Range                 |                                          |                                                                       |                        | GND<br>V <sub>A</sub> +               | V (min)<br>V (max)            |

| $V_{IN+} - V_{IN-}$                       | Differential Inpu                        | it Voltage Range                         |                                                                       |                        | -V <sub>A</sub> +<br>V <sub>A</sub> + | V (min)<br>V (max)            |

| $\frac{V_{\text{IN}+}-V_{\text{IN}-}}{2}$ | Common Mode                              | Input Voltage Range                      |                                                                       |                        | GND<br>V <sub>A</sub> +               | V (min)<br>V (max)            |

| PSS                                       | Power Supply<br>Sensitivity<br>(Note 15) |                                          | $V_A^+ = V_D^+ = 5V \pm 10\%,$<br>$V_{REF+} = 4.096V, V_{REF-} = GND$ | ±0.05<br>±0.25<br>±0.2 | ± 1.0<br>± 1.5                        | LSB (max)<br>LSB (max)<br>LSB |

| C <sub>REF</sub>                          | V <sub>REF+</sub> /V <sub>REF-</sub>     | Input Capacitance                        |                                                                       | 85                     |                                       | pF                            |

| C <sub>IN</sub>                           | Selected Multip<br>Capacitance           | lexer Channel Input                      |                                                                       | 75                     |                                       | pF                            |

**2.2.2 Converter Dynamic Characteristics** The following specifications apply only to the LM12434 and LM12438 for  $V_A{}^+=V_D{}^+=5V$ , AGND = DGND = 0V,  $V_{REF+}=4.096V$ ,  $V_{REF-}=0V$ , 12-bit + sign conversion mode,  $f_{CLK}=8.0$  MHz, throughput rate = 133.3 kHz,  $R_S=25\Omega$ , source impedance for  $V_{REF+}$  and  $V_{REF-}\leq25\Omega$ , fully-differential input with fixed 2.048V {1.25V} common-mode voltage, and minimum acquisition time unless otherwise specified. **Boldface limits apply for TA = TJ = TMIN to TMAX**; all other limits  $T_A = T_J = 25^{\circ}C$ . (Notes 6, 7, 8 and 9)

| Symbol         | Parameter                       | Conditions                                                                      | Typical<br>(Note 10)                            | Limits<br>(Note 11)                                             | Units<br>(Limit)                                |

|----------------|---------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------|

|                | CLK Duty Cycle                  |                                                                                 | 50                                              |                                                                 | %                                               |

|                |                                 |                                                                                 |                                                 | 40                                                              | % (min)                                         |

|                |                                 |                                                                                 |                                                 | 60                                                              | % (max)                                         |

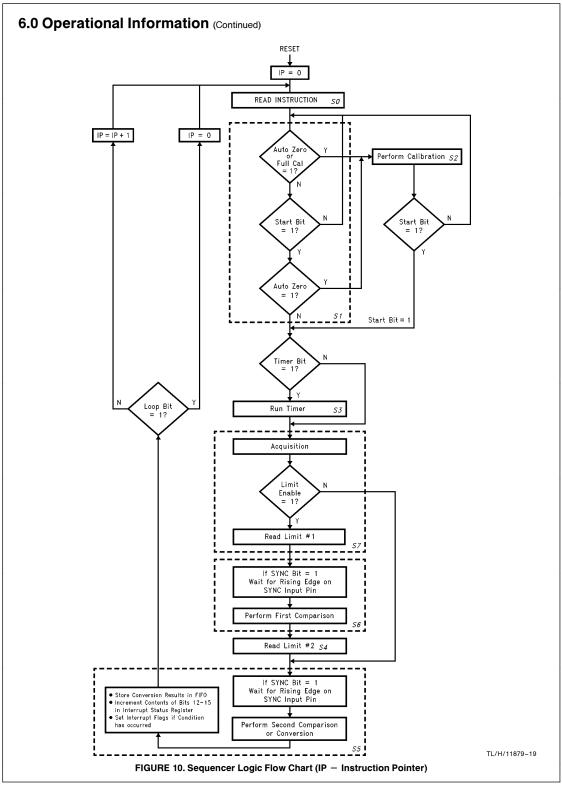

| t <sub>C</sub> | Conversion Time                 | 13-Bit Resolution,<br>Sequencer State S5 (Figure 10)                            | 44 (t <sub>CLK</sub> )                          | 44 (t <sub>CLK</sub> ) + 50 ns                                  | (max)                                           |

|                |                                 | 9-Bit Resolution,<br>Sequencer State S5 (Figure 10)                             | 21 (t <sub>CLK</sub> )                          | 21 (t <sub>CLK</sub> ) + 50 ns                                  | (max)                                           |

| t <sub>A</sub> | Acquisition Time (Programmable) | Sequencer State S7 (Figure 10) Minimum for 13-Bits Maximum for 13-Bits (D = 15) | 9 (t <sub>CLK</sub> )<br>39 (t <sub>CLK</sub> ) | 9 (t <sub>CLK</sub> ) + 50 ns<br>39 (t <sub>CLK</sub> ) + 50 ns | t <sub>CLK</sub> = CLK Period<br>(max)<br>(max) |

|                |                                 | Minimum for 9-Bits (Figure 10) Maximum for 9-Bits (D = 15)                      | 2 (t <sub>CLK</sub> )<br>2 (t <sub>CLK</sub> )  | 2 (t <sub>CLK</sub> ) + 50 ns<br>32 (t <sub>CLK</sub> ) + 50 ns | (max)<br>(max)                                  |

2.2.2 Converter Dynamic Characteristics The following specifications apply only to the LM12434 and LM12438 for  $V_A{}^+=V_D{}^+=5V$ , AGND = DGND = 0V,  $V_{REF+}=4.096V$ ,  $V_{REF-}=0V$ , 12-bit + sign conversion mode,  $f_{CLK}=8.0$  MHz, throughput rate = 133.3 kHz,  $F_{RS}=25\Omega$ , source impedance for  $F_{REF+}=100$  and  $F_{REF+}=100$  common-mode voltage, and minimum acquisition time unless otherwise specified. Boldface limits apply for  $F_{REF-}=100$  (Notes 6, 7, 8 and 9) (Continued)

| Symbol           | Parameter                                                    | Conditions                                                                                                                                                                        | Typical<br>(Note 10)     | Limits<br>(Note 11)              | Units<br>(Limit)     |

|------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------|----------------------|

| t <sub>Z</sub>   | Auto-Zero Time                                               | Sequencer State S2 (Figure 10)                                                                                                                                                    | 76 (t <sub>CLK</sub> )   | 76 (t <sub>CLK</sub> ) + 50 ns   | (max)                |

| t <sub>CAL</sub> | Full Calibration Time                                        | Sequencer State S2 (Figure 10)                                                                                                                                                    | 4944 (t <sub>CLK</sub> ) | 4944 (t <sub>CLK</sub> ) + 50 ns | (max)                |

|                  | Throughput Rate                                              | (Note 18)                                                                                                                                                                         | 142                      | 140                              | kHz<br>(min)         |

| t <sub>WD</sub>  | "Watchdog" Mode Comparison Time                              | Sequencer States S6, S4, and S5 (Figure 10)                                                                                                                                       | 11 (t <sub>CLK</sub> )   | 11 (t <sub>CLK</sub> ) + 50 ns   | (max)                |

| SNR              | Signal-to-Noise Ratio,<br>Differential Input                 | $\begin{split} V_{\text{IN}} &= \pm 4.096 \text{V (Note 20)} \\ f_{\text{IN}} &= 1 \text{ kHz} \\ f_{\text{IN}} &= 10 \text{ kHz} \\ f_{\text{IN}} &= 62 \text{ kHz} \end{split}$ | 79<br>79<br>70           |                                  | dB<br>dB<br>dB       |

| SNR              | Signal-to-Noise Ratio,<br>Single-Ended Input                 | $\begin{split} V_{\text{IN}} &= 4.096 \ V_{\text{p-p}} \\ f_{\text{IN}} &= 1 \ \text{kHz} \\ f_{\text{IN}} &= 10 \ \text{kHz} \\ f_{\text{IN}} &= 62 \ \text{kHz} \end{split}$    | 71<br>71<br>67           |                                  | dB<br>dB<br>dB       |

| SINAD            | Signal-to-Noise + Distortion Ratio,<br>Differential Input    | $\begin{split} V_{\text{IN}} &= \pm 4.096 \text{V (Note 20)} \\ f_{\text{IN}} &= 1 \text{ kHz} \\ f_{\text{IN}} &= 10 \text{ kHz} \\ f_{\text{IN}} &= 62 \text{ kHz} \end{split}$ | 79<br>78<br>67           |                                  | dB<br>dB<br>dB       |

| SINAD            | Signal-to-Noise + Distortion Ratio,<br>Single-Ended Input    | $\begin{split} V_{IN} &= 4.096  V_{p\text{-}p} \\ f_{IN} &= 1  \text{kHz} \\ f_{IN} &= 10  \text{kHz} \\ f_{IN} &= 62  \text{kHz} \end{split}$                                    | 71<br>70<br>64           |                                  | dB<br>dB<br>dB       |

| THD              | Total Harmonic Distortion,<br>Differential Input             | $\begin{array}{l} V_{IN}=\pm 4.096V \text{ (Note 20)} \\ f_{IN}=1 \text{ kHz} \\ f_{IN}=10 \text{ kHz} \\ f_{IN}=62 \text{ kHz} \end{array}$                                      | -90<br>-85<br>-71        |                                  | dBc<br>dBc<br>dBc    |

| THD              | Total Harmonic Distortion,<br>Distortion, Single-Ended Input | $\begin{aligned} &V_{IN} = 4.096  V_{p\text{-}p} \\ &f_{IN} = 1  \text{kHz} \\ &f_{IN} = 10  \text{kHz} \\ &f_{IN} = 62  \text{kHz} \end{aligned}$                                | -88<br>-82<br>-67        |                                  | dBc<br>dBc<br>dBc    |

| ENOB             | Effective Number of Bits,<br>Differential Input              | $\begin{split} &V_{\text{IN}}=\pm 4.096\text{V (Note 20)} \\ &f_{\text{IN}}=1\text{ kHz} \\ &f_{\text{IN}}=10\text{ kHz} \\ &f_{\text{IN}}=62\text{ kHz} \end{split}$             | 12.6<br>12.2<br>12.1     |                                  | Bits<br>Bits<br>Bits |

| ENOB             | Effective Number of Bits,<br>Single-Ended Input              | $\begin{split} V_{IN} &= 4.096  V_{p\text{-}p} \\ f_{IN} &= 1  \text{kHz} \\ f_{IN} &= 10  \text{kHz} \\ f_{IN} &= 62  \text{kHz} \end{split}$                                    | 11.3<br>11.2<br>10.8     |                                  | Bits<br>Bits<br>Bits |

| SFDR             | Spurious Free Dynamic Range,<br>Differential Input           | $\begin{split} V_{\text{IN}} &= \pm 4.096 \text{V (Note 20)} \\ f_{\text{IN}} &= 1 \text{ kHz} \\ f_{\text{IN}} &= 10 \text{ kHz} \\ f_{\text{IN}} &= 62 \text{ kHz} \end{split}$ | 90<br>86<br>76           |                                  | dBc<br>dBc<br>dBc    |

| SFDR             | Spurious Free Dynamic Range,<br>Single-Ended Input           | $\begin{split} V_{\text{IN}} &= 4.096 V  V_{\text{p-p}} \\ f_{\text{IN}} &= 1  \text{kHz} \\ f_{\text{IN}} &= 10  \text{kHz} \\ f_{\text{IN}} &= 62  \text{kHz} \end{split}$      | 90<br>85<br>72           |                                  | dBc<br>dBc<br>dBc    |

**2.2.2 Converter Dynamic Characteristics** The following specifications apply only to the LM12434 and LM12438 for  $V_A{}^+=V_D{}^+=5V$ , AGND = DGND = 0V,  $V_{REF+}=4.096V$ ,  $V_{REF-}=0V$ , 12-bit + sign conversion mode,  $f_{CLK}=8.0$  MHz, throughput rate = 133.3 kHz,  $R_S=25\Omega$ , source impedance for  $V_{REF+}$  and  $V_{REF-}\leq25\Omega$ , fully-differential input with fixed 2.048V common-mode voltage, and minimum acquisition time unless otherwise specified. **Boldface limits apply for T\_A = T\_J = T\_MIN to T\_{MAX}**; all other limits  $T_A=T_J=25^{\circ}C$ . (Notes 6, 7, 8 and 9) (Continued)

| Symbol          | Parameter                                                 | Conditions                                                                                                                                                                  | Typical<br>(Note 10) | Limits<br>(Note 11) | Units<br>(Limit) |

|-----------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|------------------|

| IMD             | Two Tone Intermodulation Distortion Differential Input    | $V_{IN} = \pm 4.096V$ (Note 20)<br>$f_1 = 19.190$ kHz<br>$f_2 = 19.482$ kHz                                                                                                 | -82                  |                     | dBc              |

| IMD             | Two Tone Intermodulation Distortion<br>Single Ended Input | $V_{IN} = 4.096 V_{pp}$ $f_1 = 19.190 \text{ kHz}$ $f_2 = 19.482 \text{ kHz}$                                                                                               | -80                  |                     | dBc              |

|                 | Multiplexer Channel-to-Channel Crosstalk                  | V <sub>IN</sub> = 4.096 V <sub>PP</sub><br>f <sub>IN</sub> = 5 kHz<br>f <sub>CROSSTALK</sub> = 40 kHz<br>LM12434 MUXOUT Only<br>and LM12438 MUX<br>plus Converter (Note 21) | -90                  |                     | dBc              |

| t <sub>PU</sub> | Power-Up Time                                             |                                                                                                                                                                             | 10                   |                     | ms               |

| t <sub>WU</sub> | Wake-Up Time                                              | (Note 22)                                                                                                                                                                   | 2                    |                     | ms               |

**2.2.3 DC Characteristics** The following specifications apply to the LM12434 and LM12{L}438 for  $V_A^+ = V_D^+ = 5V$  {3.3V], AGND = DGND = 0V,  $V_{REF+} = 4.096V$  {2.5V},  $V_{REF-} = 0V$ ,  $f_{CLK} = 8.0$  MHz {6 MHz} and minimum acquisition time unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A = T_J = 25^{\circ}C$ . (Notes 6, 7 and 8)

| Symbol             | Parameter                                                                            | Conditions                                                                                                                                                                                                          | Typical<br>(Note 10)                       | Limits<br>(Note 11)    | Units<br>(Limit)                             |

|--------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------|----------------------------------------------|

| I <sub>D</sub> +   | V <sub>D</sub> <sup>+</sup> Supply Current                                           | $\begin{split} f_{CLK} &= 8 \text{ MHz } \{6 \text{ MHz}\} \\ f_{SCLK} &= \text{Stopped} \\ f_{SCLK} &= 10 \text{ MHz } \{8 \text{ MHz}\} \end{split}$                                                              | 2.0 {1.4}<br>4.0 {2.0}                     | 5.0 {2.5}              | mA (max)<br>mA (max)                         |

| $I_A$ <sup>+</sup> | V <sub>A</sub> <sup>+</sup> Supply Current                                           | f <sub>CLK</sub> = 8 MHz {6 MHz}                                                                                                                                                                                    | 2.8 {2.2}                                  | 4.0 {3.5}              | mA (max)                                     |

| I <sub>ST</sub>    | Stand-By Supply Current (I <sub>D</sub> <sup>+</sup> + I <sub>A</sub> <sup>+</sup> ) | Stand-By Mode Selected  f <sub>SCLK</sub> = Stopped  f <sub>CLK</sub> = Stopped  f <sub>CLK</sub> = 8 MHz {6 MHz}  f <sub>SCLK</sub> = 10 MHz {8 MHz}  f <sub>CLK</sub> = Stopped  f <sub>CLK</sub> = 8 MHz {6 MHz} | 5{5}<br>120 {50}<br>1.4 {0.8}<br>1.4 {0.8} |                        | μΑ (max)<br>μΑ (max)<br>mA (max)<br>mA (max) |

|                    | Multiplexer ON-Channel Leakage Current                                               | V <sub>A</sub> <sup>+</sup> = 5.5V<br>ON-Channel = 5.5V<br>OFF-Channel = 0V<br>ON-Channel = 0V<br>OFF-Channel = 5.5V                                                                                                | 0.1                                        | 1.0 {3.0}<br>1.0 {3.0} | μΑ (max)<br>μΑ (max)                         |

|                    | Multiplexer OFF-Channel Leakage Current                                              | $V_A^+ = 5.5V \{3.3V\}$<br>ON-Channel = 5.5V $\{3.3V\}$<br>OFF-Channel = 0V<br>ON-Channel = 0V<br>OFF-Channel = 5.5V $\{3.3V\}$                                                                                     | 0.1                                        | 1.0 {3.0}<br>1.0 {3.0} | μΑ (max)<br>μΑ (max)                         |

**2.2.3 DC Characteristics** The following specifications apply to the LM12434 and LM12{L}438 for  $V_A{}^+ = V_D{}^+ = 5V$  {3.3V], AGND = DGND = 0V,  $V_{REF+} = 4.096V$  {2.5V},  $V_{REF-} = 0V$ ,  $f_{CLK} = 8.0$  MHz {6 MHz} and minimum acquisition time unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits  $T_A = T_J = 25^{\circ}C$ . (Notes 6, 7 and 8) (Continued)

| Symbol          | Parameter                      | Conditions      | Typical<br>(Note 10) | Limits<br>(Note 11) | Units<br>(Limit) |

|-----------------|--------------------------------|-----------------|----------------------|---------------------|------------------|

| R <sub>ON</sub> | Multiplexer ON-Resistance      | LM12434         |                      |                     |                  |

|                 |                                | $V_{IN} = 5V$   | 650                  | 1000                | $\Omega$ (max)   |

|                 |                                | $V_{IN} = 2.5V$ | 700                  | 1000                | $\Omega$ (max)   |

|                 |                                | $V_{IN} = 0V$   | 630                  | 1000                | $\Omega$ (max)   |

|                 | Multiplexer Channel-to-Channel | LM12434         |                      |                     |                  |

|                 | R <sub>ON</sub> matching       | $V_{IN} = 5V$   | ±1.0%                | ± 3.0%              | (max)            |

|                 |                                | $V_{IN} = 2.5V$ | ±1.0%                | ± 3.0%              | (max)            |

|                 |                                | $V_{IN} = 0V$   | ±1.0%                | ± 3.0%              | (max)            |

**2.2.4 Digital DC Characteristics** The following specifications apply to the LM12434 and LM12{L}438 for  $V_A^+ = V_D^+ = 5V$  {3.3V}, AGND = DGND = 0V, unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = 25°C. (Notes 6, 7 and 8)

| Symbol              | Parameter                         | Conditions                                                                   | Typical<br>(Note 10) | Limits<br>(Note 11) | Units<br>(Limit)     |

|---------------------|-----------------------------------|------------------------------------------------------------------------------|----------------------|---------------------|----------------------|

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage         | $V_A^+ = V_D^+ = 5.5V \{3.6V\}$                                              |                      | 2.0                 | V (min)              |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage         | $V_A^+ = V_D^+ = 4.5V \{3.0V\}$                                              |                      | 0.8                 | V (max)              |

| I <sub>IN(1)</sub>  | Logical "1" Input Current         | $V_{IN} = 5V \{3.3V\}$                                                       | 0.005                | 1.0                 | μΑ (max)             |

| I <sub>IN(0)</sub>  | Logical "0" Input Current         | $V_{IN} = 0V$                                                                | -0.005               | - 1.0               | μΑ (max)             |

| C <sub>IN</sub>     | All Digital Inputs                |                                                                              | 6                    |                     | pF                   |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage        | $V_A^+ = V_D^+ = 4.5V \{3.0V\}$ $I_{OUT} = -360 \mu A$ $I_{OUT} = -10 \mu A$ |                      | 2.4<br>4.25 {2.9}   | V (min)<br>V (min)   |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage        | $V_A^+ = V_D^+ = 4.5V \{3.0V\}$<br>$I_{OUT} = 1.6 \text{ mA}$                |                      | 0.4                 | V (max)              |

| lout                | TRI-STATE® Output Leakage Current | $V_{OUT} = 0V$ $V_{OUT} = 5V \{3.3V\}$                                       | -0.05<br>0.05        | -3.0<br>3.0         | μΑ (max)<br>μΑ (max) |

2.3 DIGITAL SWITCHING CHARACTERISTICS The following specifications apply to the LM12434 and LM12 $\{L\}$ 438 for  $V_A+V_D+=V_D+=5V$  {3.3V}, AGND = DGND = 0V,  $C_L$  (load capacitance) on output lines = 80 pF unless otherwise specified. Boldface limits apply for  $T_A=T_J=T_{MIN}$  to  $T_{MAX}$ , all other limits for  $T_A=T_J=25^{\circ}C$ . (Notes 6, 7, and 9)

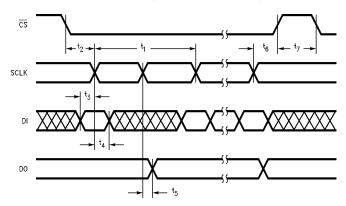

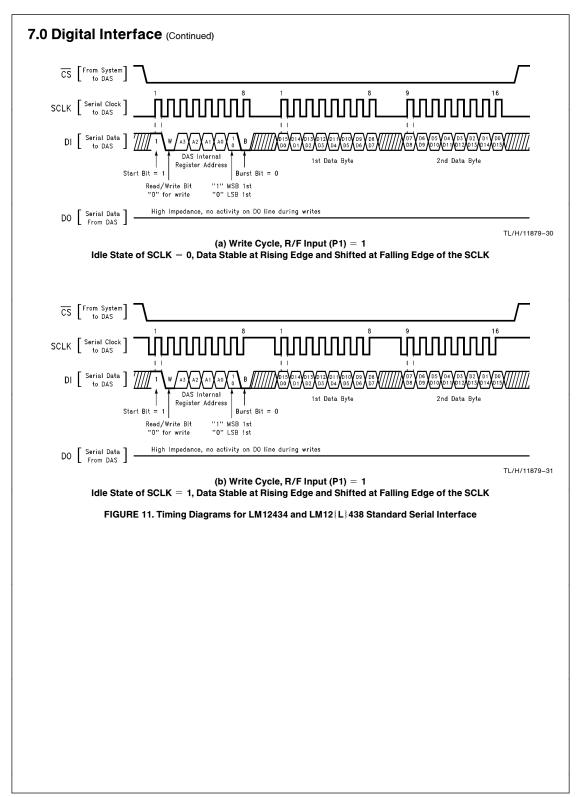

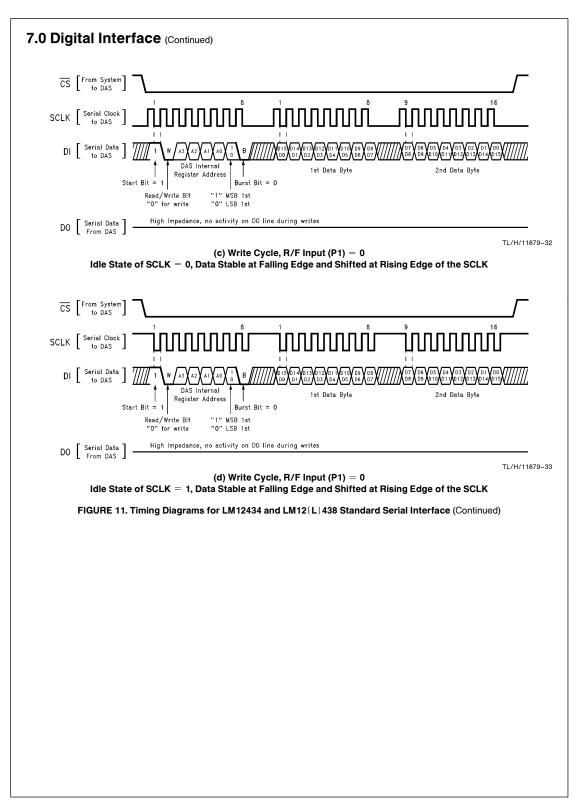

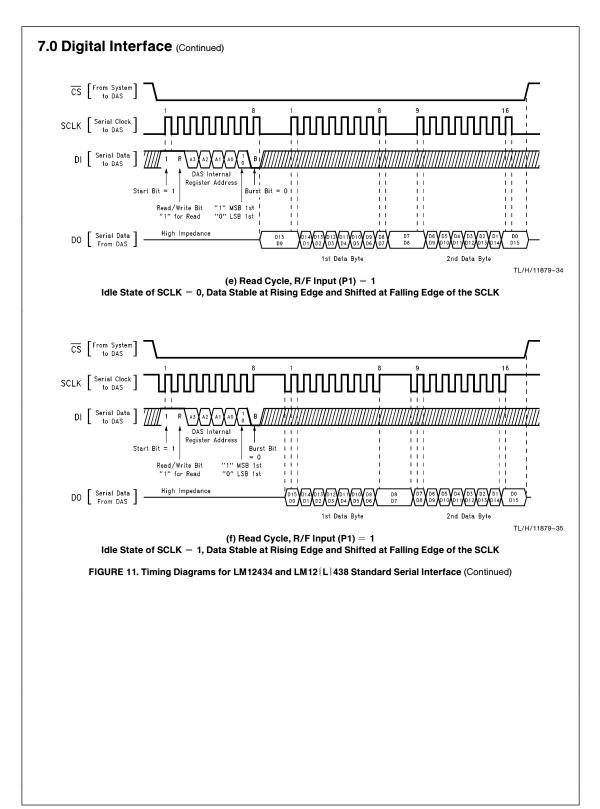

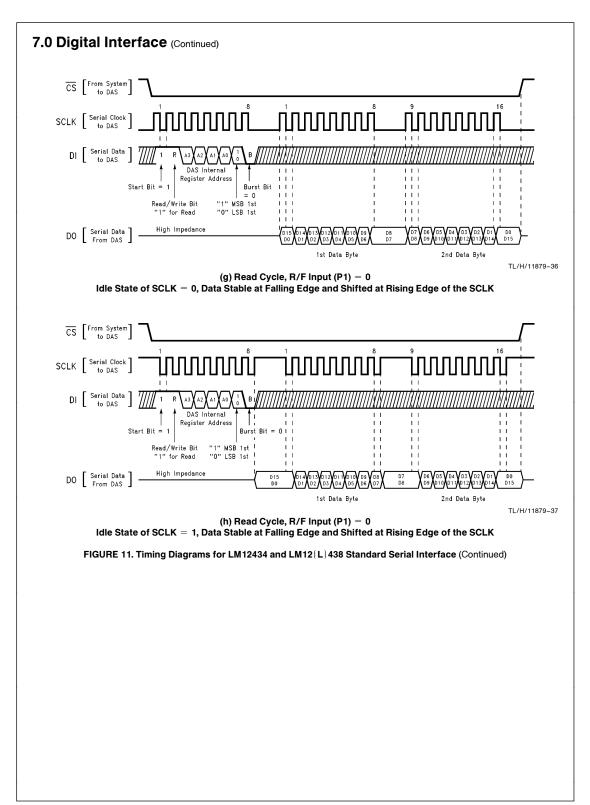

### 2.3.1 Standard Mode Interface (MICROWIRE/PLUS™, SCI and SPI/QSPI)

| Symbol<br>(See <i>Figure</i> Below) | Parameter                                                                                                     | Conditions | Typical<br>(Note 10) | Limits<br>(Note 11) | Units<br>(Limit)    |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------|------------|----------------------|---------------------|---------------------|

| t <sub>1</sub>                      | SCLK (Serial Clock) Period                                                                                    |            |                      | 100 {125}           | ns (min)            |

| t <sub>2</sub>                      | CS Set-Up Time to First<br>Clock Transition                                                                   |            |                      | 25 {30}             | ns (min)            |

| t <sub>3</sub>                      | DI Valid Set-Up Time to Data<br>Capture Transition of SCLK                                                    |            |                      | o                   | ns (min)            |

| t <sub>4</sub>                      | DI Valid Hold Time to Data<br>Capture Transition of SCLK                                                      |            |                      | 40                  | ns (min)            |

| t <sub>5</sub>                      | DO Hold Time from Data Shift<br>Transition of SCLK                                                            |            |                      | 70 {120}            | ns (max)            |

| t <sub>6</sub>                      | CS Hold Time from Last SCLK<br>Transition in a Read or Write Cycle<br>(Excluding Burst Read Cycle)            |            |                      | 25                  | ns (min)            |

| t <sub>7</sub>                      | CS Inactive to CS Active Again                                                                                |            |                      | 3                   | CLK Cycle<br>(min)* |

| t <sub>8</sub>                      | SCLK Idle Time between the End of the Command Byte Transfer and the Start of the Data Transfer in Read Cycles |            |                      | 3                   | CLK Cycle<br>(min)* |

\*CLK is the main clock input to the device, pin number 24 in PLCC package or pin number 2 in SO package.

TL/H/11879-18

2.3 DIGITAL SWITCHING CHARACTERISTICS The following specifications apply to the LM12434 and LM12{L}438 for  $V_A+V_D+=V_D+=5V$  {3.3V}, AGND = DGND = 0V,  $C_L$  (load capacitance) on output lines = 80 pF unless otherwise specified. Boldface limits apply for  $T_A=T_J=T_{MIN}$  to  $T_{MAX}$ , all other limits for  $T_A=T_J=25^{\circ}C$ . (Notes 6, 7, and 9) (Continued)

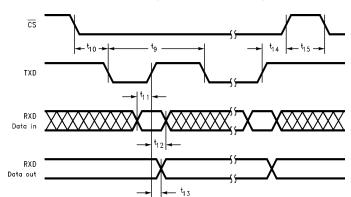

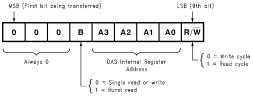

#### 2.3.2 8051 Interface Mode

| Symbol<br>(See <i>Figure</i> Below) | Parameter                                                                                                              | Conditions | Typical<br>(Note 10) | Limits<br>(Note 11) | Units<br>(Limit)    |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------|----------------------|---------------------|---------------------|

| t <sub>9</sub>                      | TXD (Serial Clock Period)                                                                                              |            |                      | 125 {250}           | ns (min)            |

| t <sub>10</sub>                     | CS Set-Up Time to First<br>Clock Transition                                                                            |            |                      | 25 {40}             | ns (min)            |

| t <sub>11</sub>                     | Data in Valid Set-Up Time to TXD Clock High                                                                            |            |                      | 40                  | ns (min)            |

| t <sub>12</sub>                     | Data in Valid Hold Time<br>from TXD Clock High                                                                         |            |                      | 40 {90}             | ns (min)            |

| t <sub>13</sub>                     | Data Out Hold Time<br>from TXD Clock High                                                                              |            |                      | 70 { 120}           | ns (max)            |

| t <sub>14</sub>                     | CS Hold Time from Last TXD<br>High in a Read or Write Cycle<br>(Excluding Burst Read Cycle)                            |            |                      | 25 {50}             | ns (min)            |

| t <sub>15</sub>                     | CS Inactive to CS Active Again                                                                                         |            |                      | 3                   | CLK Cycle (min)*    |

| t <sub>16</sub>                     | SCLK Idle Time between the<br>End of the Command Byte<br>Transfer and the Start of the<br>Data Transfer in Read Cycles |            |                      | 3                   | CLK Cycle<br>(min)* |

\*CLK is the main clock input to the device, pin number 24 in PLCC package or pin number 2 in SO package.

TL/H/11879-21

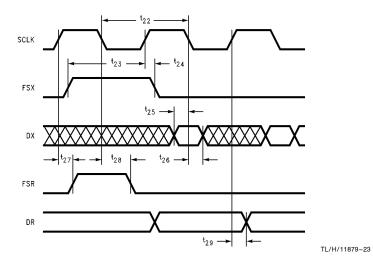

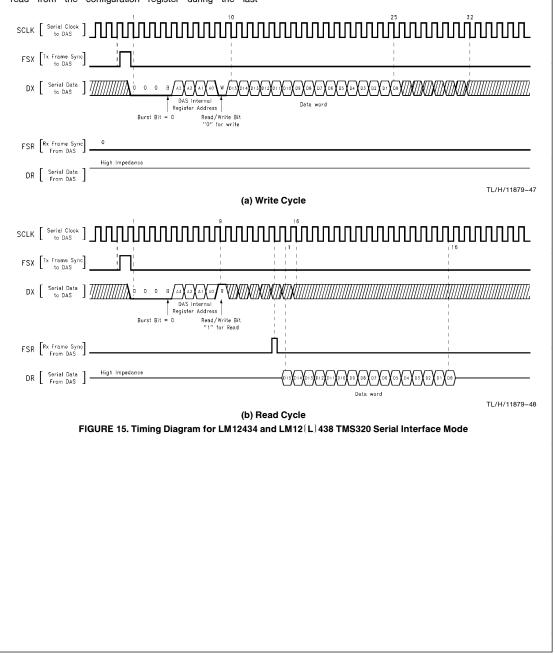

#### 2.3.3 TMS320 Interface Mode

| Symbol<br>(See <i>Figure</i> Below) | Parameter                               | Conditions | Typical<br>(Note 10) | Limits<br>(Note 11) | Units<br>(Limit) |

|-------------------------------------|-----------------------------------------|------------|----------------------|---------------------|------------------|

| t <sub>22</sub>                     | SCLK (Serial Clock) Period              |            |                      | 125 { 167 }         | ns (min)         |

| t <sub>23</sub>                     | FSX Set-Up Time to SCLK High            |            |                      | 30 (50)             | ns (min)         |

| t <sub>24</sub>                     | FSX Hold Time from SCLK High            |            |                      | 10                  | ns (min)         |

| t <sub>25</sub>                     | Data in (DX) Set-Up<br>Time to SCLK Low |            |                      | 0                   | ns (min)         |

| t <sub>26</sub>                     | Data in DX Hold Time from<br>SCLK Low   |            |                      | 30 { 120}           | ns (min)         |

| t <sub>27</sub>                     | FSR High from SCLK High                 |            |                      | 80 { 100}           | ns (max)         |

| t <sub>28</sub>                     | FSR Low from SCLK Low                   |            |                      | 120                 | ns (max)         |

| t <sub>29</sub>                     | SCLK High to Data<br>Out (DR) Change    |            |                      | 90                  | ns (max)         |

**2.3 DIGITAL SWITCHING CHARACTERISTICS** The following specifications apply to the LM12434 and LM12{L}438 for  $V_A+V_D+0$  =  $V_D+0$  = 5V {3.3V}, AGND = DGND = 0V,  $C_L$  (load capacitance) on output lines = 80 pF unless otherwise specified. **Boldface limits apply for T\_A = T\_J = T\_{MIN} to T\_{MAX},** all other limits for  $T_A = T_J = 25^{\circ}C$ . (Notes 6, 7, and 9) (Continued)

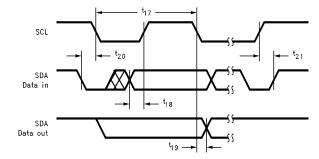

#### 2.3.4 I<sup>2</sup>C Bus Interface

The switching characteristics of the LM12434/8 for  $I^2C$  bus interface fully meets or exceeds the published specifications of the  $I^2C$  bus. The following parameters given here are the timing relationships between SCL and SDA signals related to the LM12434/8. They are not the  $I^2C$  bus specifications.

| Symbol<br>(See <i>Figure</i> Below) | Parameter                                             | Conditions | Typical<br>(Note 10) | Limits<br>(Note 11) | Units<br>(Limit) |

|-------------------------------------|-------------------------------------------------------|------------|----------------------|---------------------|------------------|

| t <sub>17</sub>                     | SCL (Clock) Period                                    |            |                      | 2500 { 10000}       | ns (min)         |

| t <sub>18</sub>                     | Data in Set-Up Time to SCL High                       |            |                      | 30                  | ns (min)         |

| t <sub>19</sub>                     | Data Out Stable after SCL Low                         |            |                      | 900 { 1400 }        | ns (max)         |

| t <sub>20</sub>                     | SDA Low Set-Up Time to SCL<br>Low (Start Condition)   |            |                      | 40                  | ns (min)         |

| t <sub>21</sub>                     | SDA High Hold Time after SCL<br>High (Stop Condition) |            |                      | 40                  | ns (min)         |

TL/H/11879-22

#### 2.4 NOTES ON SPECIFICATIONS

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified. GND specifies either AGND and/or DGND and V<sup>+</sup> specifies either V<sub>A</sub><sup>+</sup> and/or V<sub>C</sub><sup>+</sup>

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supply rails  $(V_{IN} < GND \text{ or } V_{IN} > (V_A^+ \text{ or } V_D^+))$ , the current at that pin should be limited to 5 mA. The 20 mA maximum package input current rating allows the voltage at any four pins, with an input current of 5 mA, to simultaneously exceed the power supply voltages.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$  (maximum junction temperature),  $\Theta_{JA}$  (package junction to ambient thermal resistance), and  $T_A$  (ambient temperature). The maximum allowable power dissipation at any temperature is  $PD_{max} = T_{Jmax} - T_A/V = 0$ . Of the number given in the Absolute Maximum Ratings, whichever is lower. For this device,  $T_{Jmax} = 150^{\circ}C$ , and the typical thermal resistance  $(\Theta_{JA})$  of the V package, when board mounted, is  $70^{\circ}C/W$  and in the WM package, when board mounted, is  $70^{\circ}C/W$ .

Note 5: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

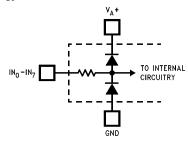

**Note 6:** Two on-chip diodes are tied to each analog input through a series resistor, as shown below. Input voltage magnitude up to 5V above  $V_A^+$  or 5V below GND will not damage the part. However, errors in the A/V conversion can occur if these diodes are forward biased by more than 100 mV. As an example, if  $V_A^+$  is  $4.5 \text{ V}_{DC}$ , the full-scale input voltage must be  $\leq 4.6 \text{ V}_{DC}$  to ensure accurate conversions.

TL/H/11879-5

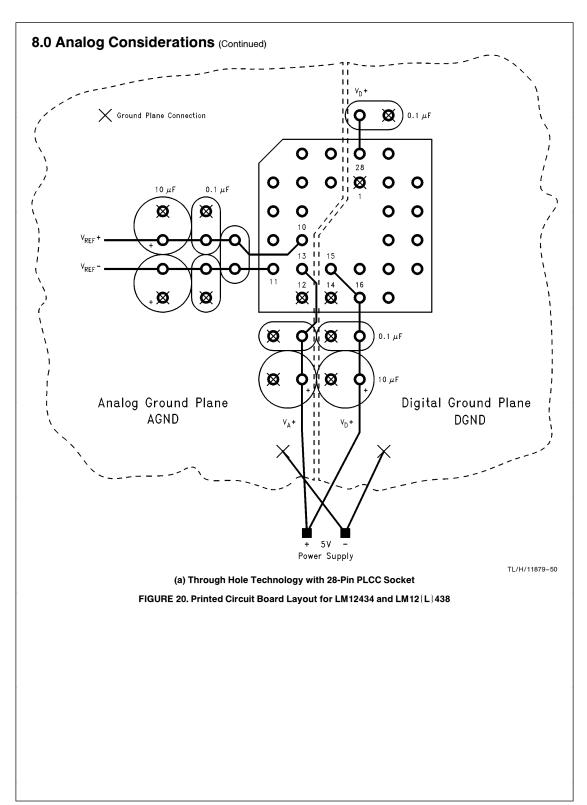

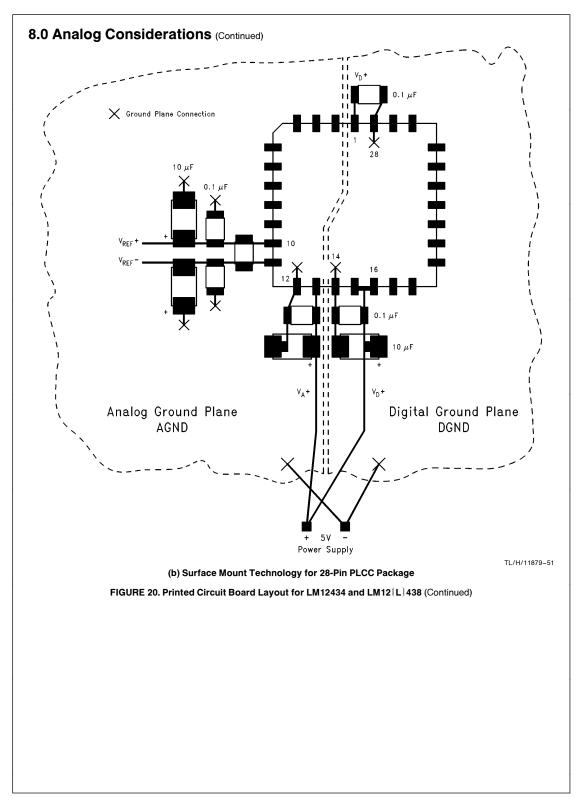

Note 7:  $V_A^+$  and  $V_D^+$  must be connected together to the same power supply voltage and bypassed with separate capacitors at each  $V^+$  pin to assure conversion/comparison accuracy. Refer to Section 8.0 for a detailed discussion on grounding the DAS.

Note 8: Accuracy is guaranteed when operating the LM12434/LM12{L}438 at  $f_{CLK} = 8$  MHz {6 MHz}.

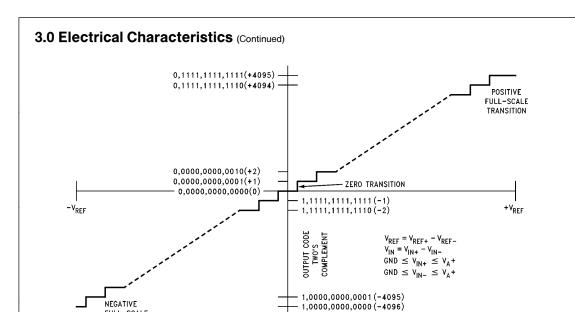

Note 9: With the test condition for V<sub>REF</sub> (V<sub>REF+</sub> - V<sub>REF-</sub>) given as +4.096V, the 12-bit LSB is 1 mV and the 8-bit/"Watchdog" LSB is 19 mV.

Note 10: Typicals are at  $T_A = 25^{\circ}\text{C}$  and represent most likely parametric norm.

Note 11: Limits are guaranteed to National's AOQL (Average Output Quality Level).

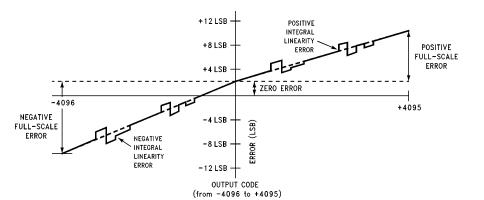

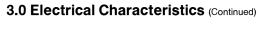

Note 12: Positive integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive full-scale and zero. For negative integral linearity error the straight line passes through negative full-scale and zero. (See Figures 5b and 5c).

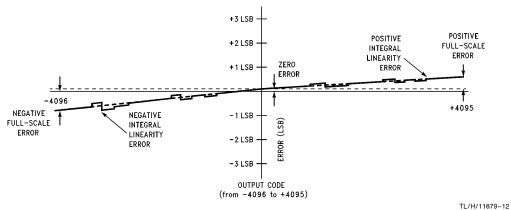

Note 13: Zero error is a measure of the deviation from the mid-scale voltage (a code of zero), expressed in LSB. It is the average value of the code transitions between -1 to 0 and 0 to +1 (see Figure 6).

Note 14: The DC common-mode error is measured with both the inverted and non-inverted inputs shorted together and driven from 0V to 5V {3.3V}. The measured value is referred to the resulting output value when the inputs are driven with a 2.5V {1.65V} signal.

Note 15: Power Supply Sensitivity is measured after Auto-Zero and/or Auto-Calibration cycle has been completed with  $V_A^+$  and  $V_D^+$  at the specified extremes.

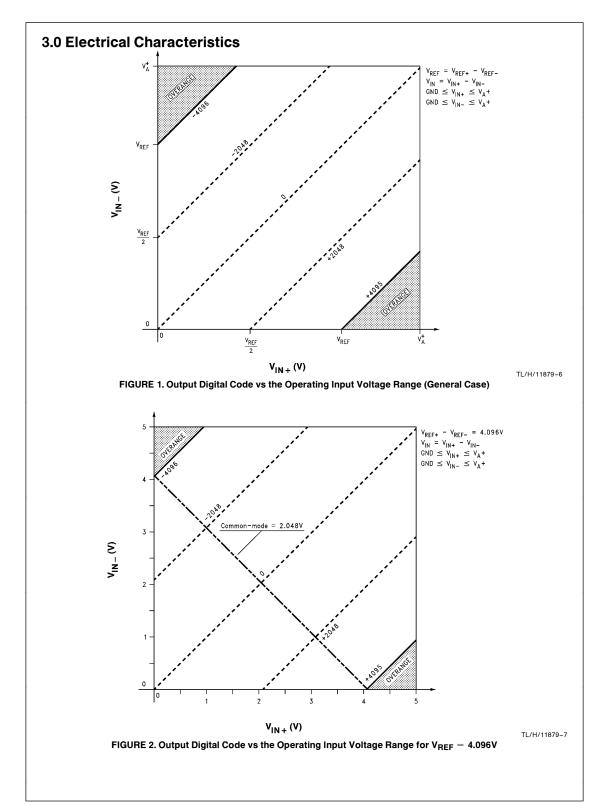

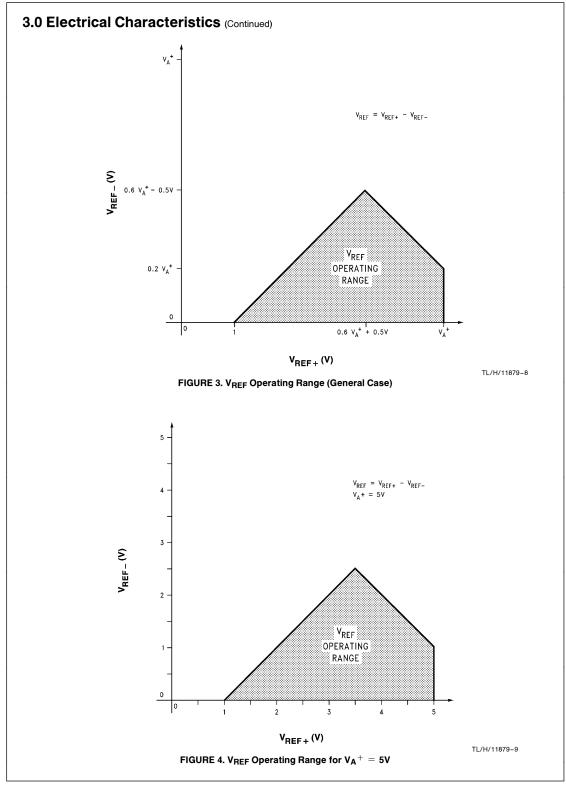

Note 16:  $V_{REFCM}$  (Reference Voltage Common Mode Range) is defined as  $(V_{REF+} + V_{REF-})/2$ . See Figures 3 and 4.

Note 17: The device self-calibration technique ensures linearity and offset errors as specified, but noise inherent in the self-calibration process will result in a repeatability uncertainty of ±0.10 LSB.

Note 18: The Throughput Rate is for a single instruction repeated continuously while reading data during conversions with a serial clock frequency f<sub>SCLK</sub> = 10 MHz {8 MHz}. Sequencer states 0 (1 clock cycle), 1 (1 clock cycle), 7 (9 clock cycles) and 5 (44 clock cycles) are used (see *Figure 10*) for a total of 56 clock cycles per conversion. The Throughput Rate is f<sub>CLK</sub> (MHz)/N, where N is the number of clock cycles/conversion.

Note 19: See AN-450 "Surface Mounting Methods and their Effect on Product Reliability" for other methods of soldering surface mount devices.

Note 20: Each input referenced to the other input sees a  $\pm 4.096V$  (8.192  $V_{p-p}$ ) sine wave. However the voltage at each input stays within the supply rails. This is done by applying two sine waves with 180° phase shift and 4.096  $V_{p-p}$  (between GND and  $V_A^+$ ) to the inputs.

Note 21: Multiplexer channel-to-channel crosstalk is measured by placing a sinewave with a frequency of  $f_{\rm IN} = 5$  kHz on one channel and another sinewave with a frequency of  $f_{\rm CROSSTALK} = 40$  kHz on the remaining channels. 8192 conversions are performed on the channel with the 5 kHz signal. A special response is generated by doing a FFT on these samples. The crosstalk is then calculated by subtracting the amplitude of the frequency component at 40 kHz from the amplitude of the fundamental frequency at 5 kHz.

Note 22: Interrupt 7 is set to return an out-of-standby flag 10 ms (typ) after the device is requested to come out of standby mode. However, characterization has shown the devices will perform to their rated specifications in 2 ms.

FIGURE 5a. Transfer Characteristic

TL/H/11879-10

TL/H/11879-11

ANALOG INPUT VOLTAGE  $(V_{IN})$

NEGATIVE FULL-SCALE TRANSITION

FIGURE 5b. Simplified Error Curve vs Output Code without Auto-Calibration or Auto-Zero Cycles

FIGURE 5c. Simplified Error Curve vs Output Code after Auto-Calibration Cycle

FIGURE 6. Offset or Zero Error Voltage

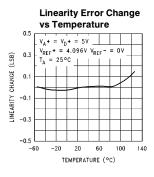

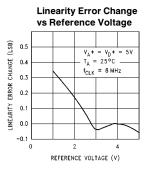

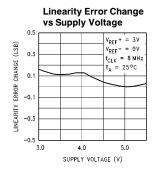

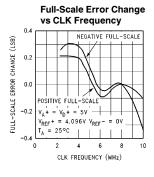

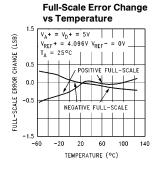

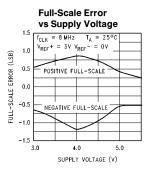

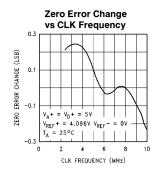

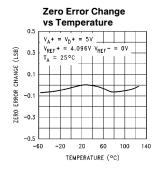

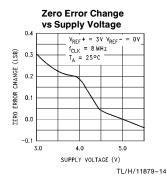

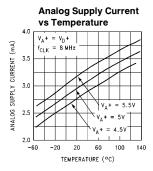

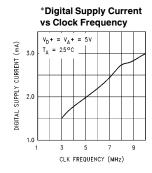

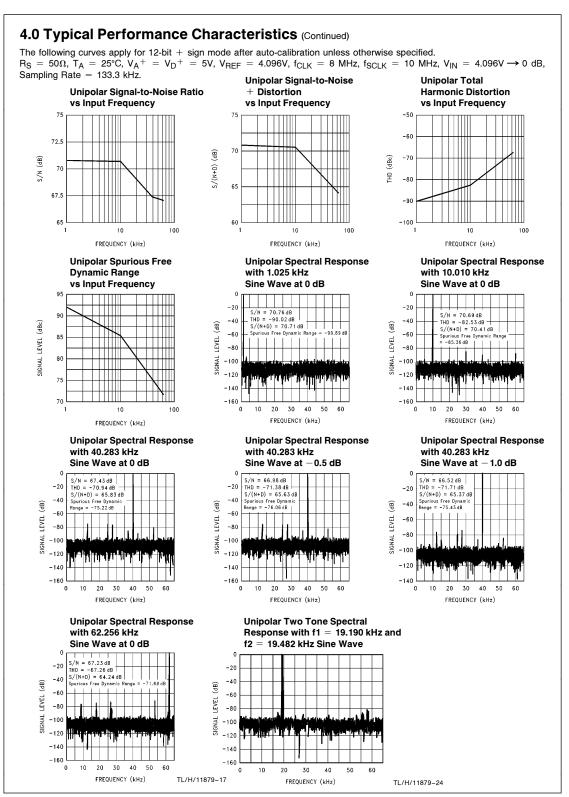

### **4.0 Typical Performance Characteristics**

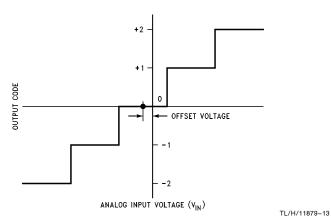

The following curves apply for 12-bit + sign mode after auto-calibration unless otherwise specified. The performance for 8-bit + sign and "watchdog" modes is equal to or better than shown. (Note 9)

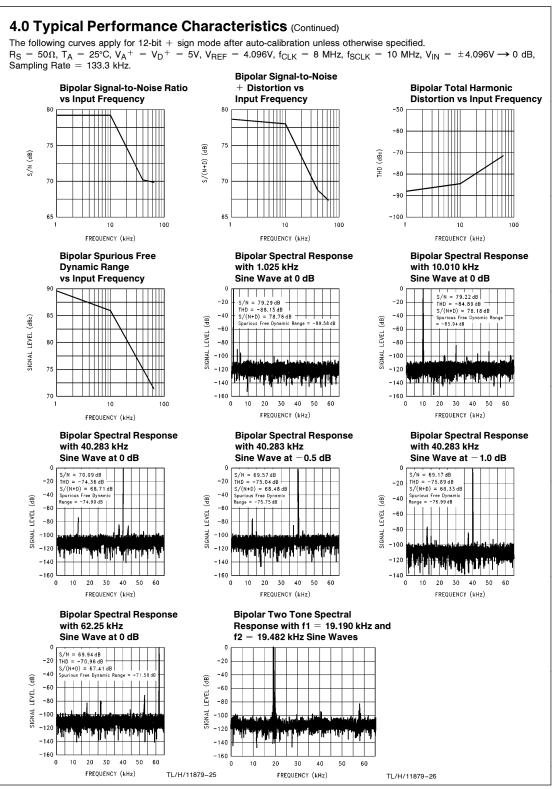

### 4.0 Typical Performance Characteristics (Continued)

The following curves apply for 12-bit + sign mode after auto-calibration unless otherwise specified. The performance for 8-bit + sign and "watchdog" modes is equal to or better than shown. (Note 9)

\*Free-running conversion and SPI mode data read at 200 ns SCLK period.

TL/H/11879-15

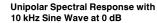

The following curves apply to the LM12L438 in 12-bit + sign mode after auto-calibration unless otherwise specified.  $R_S = 50\Omega$ ,  $T_A = 25^{\circ}\text{C}$ ,  $V_A^+ = V_D^+ = 3.3\text{V}$ ,  $V_{REF} = 2.5\text{V}$ ,  $f_{CLK} = 6$  MHz,  $f_{SCLK} = 8$  MHz,  $f_{SCL$

# Unipolar Spectral Response with 20 kHz Sine Wave at 0 dB

TL/H/11879-84

The following curves apply for 12-bit + sign mode after auto-calibration unless otherwise specified.  $R_S = 50\Omega$ ,  $T_A = 25^{\circ}C$ ,  $V_A^+ = V_D^+ = 5V$ ,  $V_{REF} = 4.096V$ ,  $f_{CLK} = 8$  MHz,  $f_{SCLK} = 10$  MHz,  $V_{IN} = 4.096V \rightarrow 0$  dB, Sampling Rate = 100 kHz.

### Unipolar Special Response with 41.2 kHz Sine Wave at 0 dB Reading Data

TL/H/11879-55

# 5.0 Pin Descriptions

TABLE I. LM12{L}438 Pin Description

| Pin Nu                               | mber                                 |                                               | `                                                                                                                                                                                                                                                                                                                                                                                                          | .}438 PIN Descript                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|--------------------------------------|--------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| PLCC<br>Pkg.                         | SO<br>Pkg.                           | Pin Name                                      |                                                                                                                                                                                                                                                                                                                                                                                                            | Descr                                                                                                                                                                                                                                                                                                                                                                              | ription                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 1                                    | 7                                    | DGND                                          | " "                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                    | ground connection. It should be connected bund return to the system power supply.                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | 8<br>9<br>10<br>11<br>12<br>13<br>14 | IN0<br>IN1<br>IN2<br>IN3<br>IN4<br>IN5<br>IN6 | active channels are selected channel can be selected for a                                                                                                                                                                                                                                                                                                                                                 | These are the eight analog inputs to the multiplexer. For each conversion to be performed, the active channels are selected according to the instruction RAM programming. Any individual channel can be selected for a single-ended conversion referenced to AGND, or any pair of channels, whether adjacent or non adjacent, can be selected as a fully differential input pairs. |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| 10                                   | 16                                   | V <sub>REF</sub> <sup>+</sup>                 | Figures 3 and 4). In order to a at least with a parallel combin                                                                                                                                                                                                                                                                                                                                            | Positive reference input. The operating voltage range for this input is $1V \le V_{REF}^+ \le V_A^+$ (See Figures 3 and 4). In order to achieve 12-bit performance this pin should be by passed to AGND at least with a parallel combination of a 10 $\mu$ F and a 0.1 $\mu$ F (ceramic) capacitor. The capacitors should be placed as close to the part as possible.              |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| 11                                   | 17                                   | V <sub>REF</sub> -                            | Negative reference input. The operating voltage range for this input is 0 V $\leq$ V <sub>REF</sub> $^ \leq$ V <sub>REF</sub> $^+$ $-$ 1V (See Figures 3 and 4). In order to achieve 12-bit performance, this pin should be bypassed to AGND at least with a parallel combination of a 10 $\mu$ F and a 0.1 $\mu$ F (ceramic) capacitor. The capacitors should be placed as close to the part as possible. |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| 12                                   | 18                                   | AGND                                          |                                                                                                                                                                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                                                                                                                                                                                                  | ly ground connection. It should be connected<br>ound return to the system power supply.                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 13                                   | 19                                   | V <sub>A</sub> +                              | voltage range is +3.0V to +9 connected to the same poten                                                                                                                                                                                                                                                                                                                                                   | 5.5V. Accuracy is g<br>tial. In order to ach<br>ith a parallel combi                                                                                                                                                                                                                                                                                                               | the analog circuitry. The device operating supply uaranteed only if the ${\rm V_A}^+$ and ${\rm V_D}^+$ are ieve 12-bit performance, this pin should be nation of a 10 $\mu{\rm F}$ and a 0.1 $\mu{\rm F}$ (ceramic) lose to the part as possible. |  |  |  |  |  |  |  |  |

| 14                                   | 20                                   | DGND                                          | Digital ground. See above de                                                                                                                                                                                                                                                                                                                                                                               | inition.                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| 15<br>16                             | 21<br>22                             | V <sub>D</sub> +                              | voltage range is +3.0V to +9                                                                                                                                                                                                                                                                                                                                                                               | 5.5V. The device acotential. In order to with a parallel comb                                                                                                                                                                                                                                                                                                                      | he analog circuitry. The device operating supply couracy is guaranteed only if the $V_A{}^+$ and $V_D{}^+$ achieve 12-bit performance this pin should be sination of a 10 $\mu$ F and a 0.1 $\mu$ F (ceramic) lose to the part as possible.        |  |  |  |  |  |  |  |  |

| 17                                   | 23                                   | P5                                            | P1-P5 are the multi-function<br>depending on the selected m<br>Serial interface input:                                                                                                                                                                                                                                                                                                                     | •                                                                                                                                                                                                                                                                                                                                                                                  | ut or output pins that have different assignments  SCLK  TXD  SCL  DR                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 18                                   | 24                                   | P4                                            | Serial interface input/output:                                                                                                                                                                                                                                                                                                                                                                             | Standard:<br>8051:<br>I <sup>2</sup> C:<br>TMS320:                                                                                                                                                                                                                                                                                                                                 | DO<br>RXD<br>SDA<br>DR                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| 19                                   | 25                                   | P3                                            | Serial interface input:                                                                                                                                                                                                                                                                                                                                                                                    | Standard:<br>8051:<br>I <sup>2</sup> C:<br>TMS320:                                                                                                                                                                                                                                                                                                                                 | DI<br>CS<br>SAD2<br>DX                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

# 5.0 Pin Descriptions (Continued)

TABLE I. LM12{L}438 Pin Description (Continued)

| Pin Nu       | mber       |                      | Description                                                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|--------------|------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

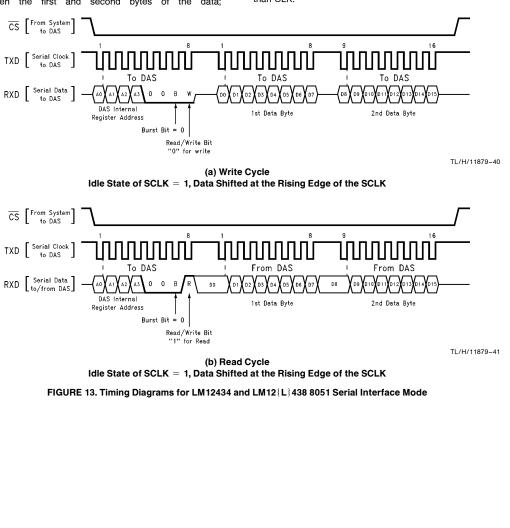

| PLCC<br>Pkg. | SO<br>Pkg. | Pin Name             |                                                                                                                                                           | Descr                                                                                                                                                            | iption                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |