# Dual-Channel, Audio Difference Amplifier

**AD8273**

#### **FEATURES**

Two gain settings

Gain of ½ (–6 dB)

Gain of 2 (+6 dB)

0.05% maximum gain error

10 ppm maximum gain drift

Excellent ac specifications

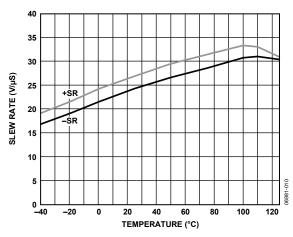

20 V/µs minimum slew rate

800 ns to 0.01% settling time

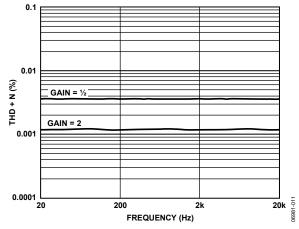

Low distortion: 0.004%, 20 Hz to 20 kHz

High accuracy dc performance

77 dB minimum CMRR

14-lead SOIC package

Supply current: 2.5 mA maximum per channel

700 µV maximum offset voltage

Supply range: ±2.5 V to ±18 V

#### **APPLICATIONS**

High performance audio Instrumentation amplifier building blocks Level translators Automatic test equipment Sin/Cos encoders

#### **GENERAL DESCRIPTION**

The AD8273 is a low distortion, dual-channel amplifier with internal gain setting resistors. With no external components, it can be configured as a high performance difference amplifier ( $G = \frac{1}{2}$  or 2), inverting amplifier ( $G = \frac{1}{2}$  or 2), or noninverting amplifier ( $G = \frac{1}{2}$  or 3).

The AD8273 operates on both single and dual supplies and only requires 2.5 mA maximum supply current for each amplifier. It is specified over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C and is fully RoHS compliant.

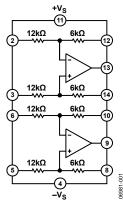

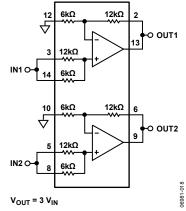

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Table 1. Difference Amplifiers by Category

| Low<br>Distortion | High<br>Voltage | Single-Supply<br>Unidirectional | Single-Supply<br>Bidirectional |

|-------------------|-----------------|---------------------------------|--------------------------------|

| AD8270            | AD628           | AD8202                          | AD8205                         |

| AD8273            | AD629           | AD8203                          | AD8206                         |

| AMP03             |                 |                                 | AD8216                         |

# **AD8273**

## **TABLE OF CONTENTS**

| Features                  | 1 |

|---------------------------|---|

| Applications              | 1 |

| General Description       | 1 |

| Functional Block Diagram  | 1 |

| Revision History          | 2 |

| Specifications            | 3 |

| Absolute Maximum Ratings  | 4 |

| Maximum Power Dissipation | 4 |

| FSD Caution               | 4 |

| Pin Configuration and Function Descriptions |

|---------------------------------------------|

| Typical Performance Characteristics         |

| Theory of Operation                         |

| Configurations1                             |

| Power Supplies1                             |

| Outline Dimensions                          |

| Ordering Guide1                             |

### **REVISION HISTORY**

1/08—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{\text{S}}=\pm15$  V,  $V_{\text{REF}}=0$  V,  $T_{\text{A}}=25^{\circ}\text{C},$   $G=\frac{1}{2}$ ,  $R_{\text{L}}=2$  kO, unless otherwise noted.

Table 2.

| Parameter                                 | Conditions                                                         | Min             | Тур   | Max           | Unit   |

|-------------------------------------------|--------------------------------------------------------------------|-----------------|-------|---------------|--------|

| DYNAMIC PERFORMANCE                       |                                                                    |                 |       |               |        |

| Bandwidth                                 |                                                                    |                 | 20    |               | MHz    |

| Slew Rate                                 |                                                                    | 20              |       |               | V/µs   |

| Settling Time to 0.1%                     | 10 V step on output, $C_L = 100 \text{ pF}$                        |                 | 670   | 750           | ns     |

| Settling Time to 0.01%                    | 10 V step on output, C <sub>L</sub> = 100 pF                       |                 | 750   | 800           | ns     |

| Channel Separation                        | f = 1 kHz                                                          |                 | 130   |               | dB     |

| NOISE/DISTORTION <sup>1</sup>             |                                                                    |                 |       |               |        |

| THD + Noise                               | $f = 1 \text{ kHz}$ , $V_{OUT} = 10 \text{ V p-p}$ , 600 Ω load    |                 | 0.004 |               | %      |

| Noise Floor, RTO <sup>2</sup>             | 20 kHz BW                                                          |                 | -106  |               | dBu    |

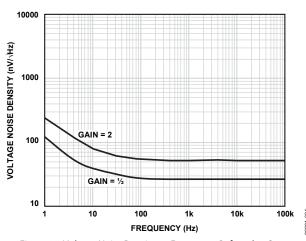

| Output Voltage Noise (Referred to Output) | f = 20 Hz to 20 kHz                                                |                 | 3.5   |               | μV rms |

|                                           | f = 1 kHz                                                          |                 | 26    |               | nV/√Hz |

| GAIN                                      |                                                                    |                 |       |               |        |

| Gain Error                                |                                                                    |                 |       | 0.05          | %      |

| Gain Drift                                | −40°C to +85°C                                                     |                 | 2     | 10            | ppm/°C |

| Gain Nonlinearity                         | $V_{OUT} = 10 \text{ V p-p, } 600 \Omega \text{ load}$             |                 | 200   |               | ppm    |

|                                           | $V_{OUT} = 5 \text{ V p-p, } 600 \Omega \text{ load}$              |                 | 50    |               | ppm    |

| INPUT CHARACTERISTICS                     |                                                                    |                 |       |               |        |

| Offset <sup>3</sup>                       | Referred to output                                                 |                 | 100   | 700           | μV     |

| vs. Temperature                           | −40°C to +85°C                                                     |                 | 3     |               | μV/°C  |

| vs. Power Supply                          | $V_S = \pm 2.5 \text{ V to } \pm 18 \text{ V}$                     |                 | 2     | 10            | μV/V   |

| Common-Mode Rejection Ratio               | $V_{CM} = \pm 40 \text{ V}$ , $R_S = 0 \Omega$ , referred to input | 77              | 86    |               | dB     |

| Input Voltage Range⁴                      |                                                                    | $-3V_{S} + 4.5$ |       | $+3V_{S}-4.5$ | V      |

| Impedance <sup>5</sup>                    |                                                                    |                 |       |               |        |

| Differential                              | $V_{CM} = 0 V$                                                     |                 | 36    |               | kΩ     |

| Common Mode <sup>6</sup>                  |                                                                    |                 | 9     |               | kΩ     |

| OUTPUT CHARACTERISTICS                    |                                                                    |                 |       |               |        |

| Output Swing                              |                                                                    | $-V_{s} + 1.5$  |       | $+V_{S}-1.5$  | V      |

| Short-Circuit Current Limit               | Sourcing                                                           |                 | 100   |               | mA     |

|                                           | Sinking                                                            |                 | 60    |               | mA     |

| Capacitive Load Drive                     | G = ½                                                              |                 | 200   |               | pF     |

|                                           | G = 2                                                              |                 | 1200  |               | pF     |

| POWER SUPPLY                              |                                                                    |                 |       |               |        |

| Supply Current (per Amplifier)            |                                                                    |                 |       | 2.5           | mA     |

| TEMPERATURE RANGE                         |                                                                    |                 |       |               |        |

| Specified Performance                     |                                                                    | -40             |       | +85           | °C     |

$<sup>^1</sup>$  Includes amplifier voltage and current noise, as well as noise of internal resistors.  $^2$  dBu = 20 log (V rms /0.7746).  $^3$  Includes input bias and offset current errors.

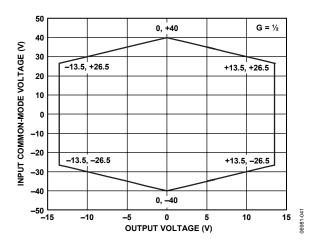

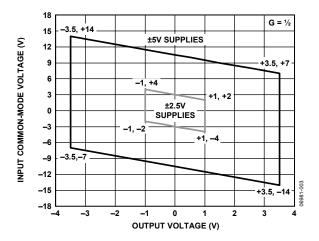

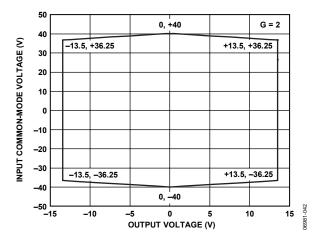

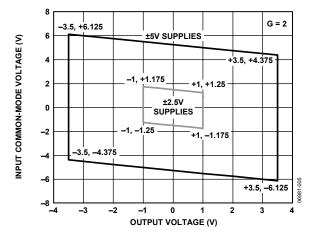

<sup>4</sup> May also be limited by absolute maximum input voltage or by the output swing. See the Absolute Maximum Ratings section and Figure 9 through Figure 12 for

$<sup>^{\</sup>text{5}}$  Internal resistors are trimmed to be ratio matched but have  $\pm 20\%$  absolute accuracy.

$<sup>^6</sup>$  Common mode is calculated looking into both inputs. Common-mode impedance looking into only one input is 18 k $\Omega$ .

## **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                                    | Rating                 |

|----------------------------------------------|------------------------|

|                                              | <del></del>            |

| Supply Voltage                               | ±18 V                  |

| Output Short-Circuit Current                 | Observe derating curve |

| Voltage at Any Input Pin                     | 40 V                   |

| Differential Input Voltage                   | 40 V                   |

| Current into Any Input Pin                   | 3 mA                   |

| Storage Temperature Range                    | −65°C to +130°C        |

| Specified Temperature Range                  | −40°C to +85°C         |

| Thermal Resistance                           |                        |

| $	heta_{JA}$                                 | 105°C/W                |

| $	heta_{JC}$                                 | 36°C/W                 |

| Package Glass Transition Temperature $(T_G)$ | 150°C                  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

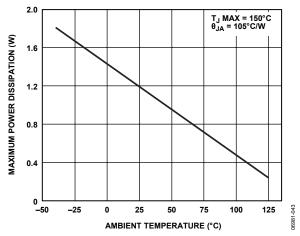

#### **MAXIMUM POWER DISSIPATION**

The maximum safe power dissipation for the AD8273 is limited by the associated rise in junction temperature (T<sub>1</sub>) on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit may change the stresses that the package exerts on the die, permanently shifting the parametric performance of the amplifiers. Exceeding a temperature of 150°C for an extended period can result in a loss of functionality.

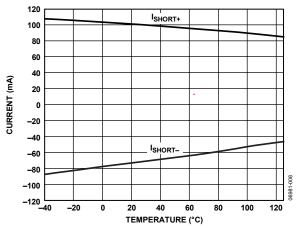

The AD8273 has built-in, short-circuit protection that limits the output current to approximately 100 mA (see Figure 2 for more information). While the short-circuit condition itself does not damage the part, the heat generated by the condition can cause the part to exceed its maximum junction temperature, with corresponding negative effects on reliability.

Figure 2. Maximum Power Dissipation vs. Ambient Temperature

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

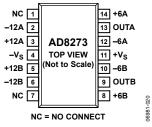

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                              |

|---------|----------|--------------------------------------------------------------------------|

| 1, 7    | NC       | No Connect.                                                              |

| 2       | -12A     | The 12 $k\Omega$ resistor connects to the negative terminal of Op Amp A. |

| 3       | +12A     | The 12 $k\Omega$ resistor connects to the positive terminal of Op Amp A. |

| 4       | -Vs      | Negative Supply.                                                         |

| 5       | +12B     | The 12 $k\Omega$ resistor connects to the positive terminal of Op Amp B. |

| 6       | -12B     | The 12 $k\Omega$ resistor connects to the negative terminal of Op Amp B. |

| 8       | +6B      | The 6 $k\Omega$ resistor connects to the positive terminal of Op Amp B.  |

| 9       | OUTB     | Op Amp B Output.                                                         |

| 10      | -6B      | The 6 $k\Omega$ resistor connects to the negative terminal of Op Amp B.  |

| 11      | +Vs      | Positive Supply.                                                         |

| 12      | -6A      | The 6 $k\Omega$ resistor connects to the negative terminal of Op Amp A.  |

| 13      | OUTA     | Op Amp A Output.                                                         |

| 14      | +6A      | The 6 $k\Omega$ resistor connects to the positive terminal of Op Amp A.  |

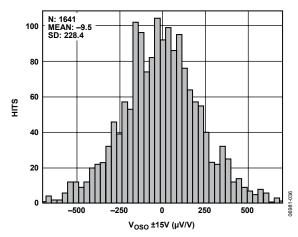

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_S = \pm 15 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ ,  $G = \frac{1}{2}$ , difference amplifier configuration, unless otherwise noted.

Figure 4. Typical Distribution of System Offset Voltage,  $G = \frac{1}{2}$ , Referred to Output

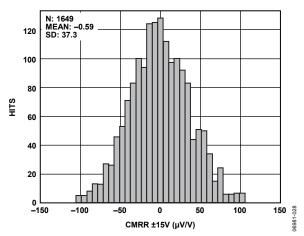

Figure 5. Typical Distribution of CMRR,  $G = \frac{1}{2}$ , Referred to Input

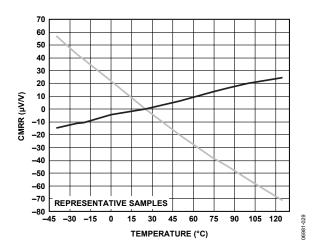

Figure 6. CMRR vs. Temperature, Normalized at 25°C

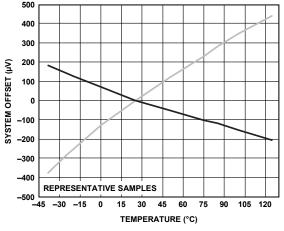

Figure 7. System Offset vs. Temperature, Normalized at 25°C, Referred to Output

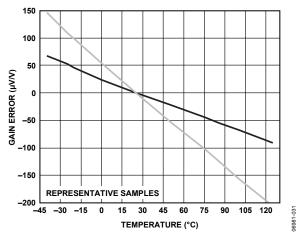

Figure 8. Gain Error vs. Temperature, Normalized at 25°C

Figure 9. Input Common-Mode Voltage vs. Output Voltage, Gain = ½, ±15 V Supplies

Figure 10. Input Common-Mode Voltage vs. Output Voltage, Gain =  $\frac{1}{2}$ ,  $\pm 5$  V and  $\pm 2.5$  V Supplies

Figure 11. Input Common-Mode Voltage vs. Output Voltage,  $Gain = 2, \pm 15 \text{ V Supplies}$

Figure 12. Input Common-Mode Voltage vs. Output Voltage,  $Gain = 2, \pm 5 V \text{ and } \pm 2.5 V \text{ Supplies}$

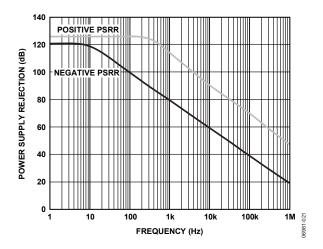

Figure 13. Power Supply Rejection vs. Frequency,  $G = \frac{1}{2}$ , Referred to Output

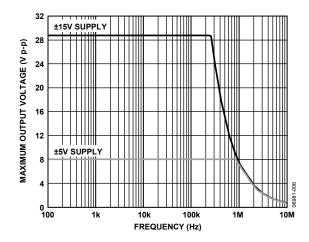

Figure 14. Maximum Output Voltage vs. Frequency

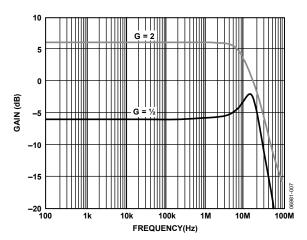

Figure 15. Gain vs. Frequency

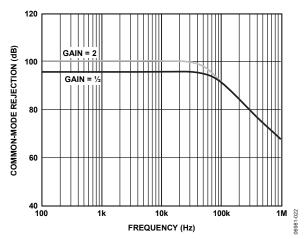

Figure 16. Common-Mode Rejection vs. Frequency, Referred to Input

Figure 17. Short-Circuit Current vs. Temperature

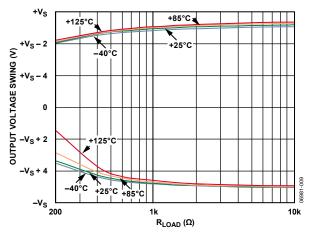

Figure 18. Output Voltage Swing vs.  $R_{LOAD}$ ,  $V_S = \pm 15 \text{ V}$

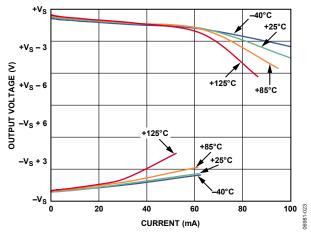

Figure 19. Output Voltage vs. IOUT

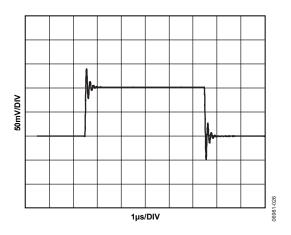

Figure 20. Small Signal Step Response, Gain = 2

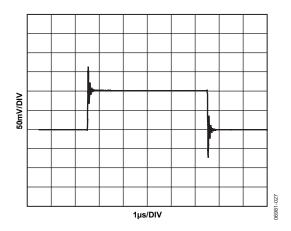

Figure 21. Small Signal Step Response, Gain = 1/2

Figure 22. Small Signal Pulse Response with 500 pF Capacitor Load, Gain = 2

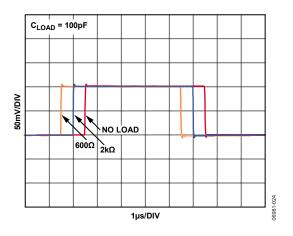

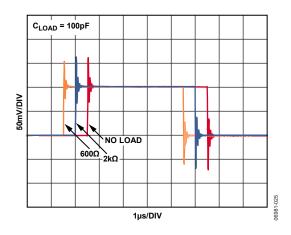

Figure 23. Small Signal Pulse Response for 100 pF Capacitive Load, Gain = ½

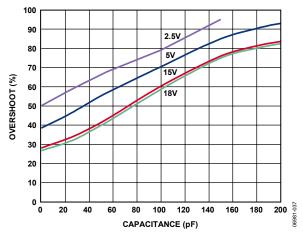

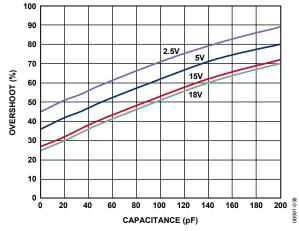

Figure 24. Small Signal Overshoot vs. Capacitive Load,  $G = \frac{1}{2}$ , No Resistive Load

Figure 25. Small Signal Overshoot vs. Capacitive Load,  $G = \frac{1}{2}$ , 600  $\Omega$  in Parallel with Capacitive Load

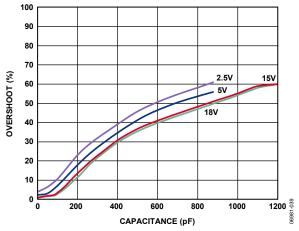

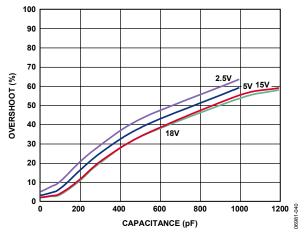

Figure 26. Small Signal Overshoot vs. Capacitive Load, G = 2, No Resistive Load

Figure 27. Small Signal Overshoot vs. Capacitive Load,  $G = 2,600 \Omega$  in Parallel with Capacitive Load

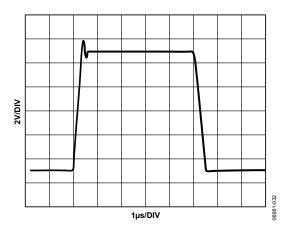

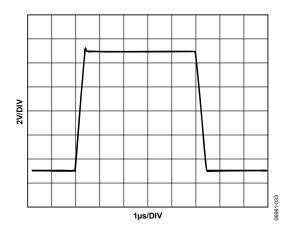

Figure 28. Large Signal Pulse Response Gain =  $\frac{1}{2}$

Figure 29. Large Signal Pulse Response, Gain = 2

Figure 30.Slew Rate vs. Temperature

Figure 31. THD+N vs. Frequency,  $V_{OUT} = 10 \text{ V p-p}$

Figure 32. Voltage Noise Density vs. Frequency, Referred to Output

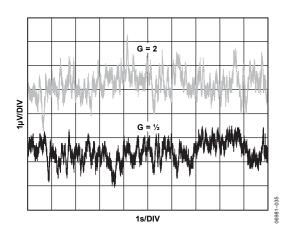

Figure 33. 0.1 Hz to 10 Hz Voltage Noise, RTO

## THEORY OF OPERATION

The AD8273 has two channels, each consisting of a high precision, low distortion op amp and four trimmed resistors. Although such a circuit can be built discretely, placing the resistors on the chip offers advantages to board designers that include better dc specifications, better ac specification, and lower production costs.

The resistors on the AD8273 are laser trimmed and tightly matched. Specifications that depend on the resistor matching, such as gain drift, common-mode rejection, and gain accuracy, are better than can be achieved with standard discrete resistors.

The positive and negative input terminals of the AD8273 op amp are not pinned out intentionally. Keeping these nodes internal means their capacitance is considerably lower than it would be in discrete designs. Lower capacitance at these nodes means better loop stability and improved common-mode rejection vs. frequency.

The internal resistors of the AD8273 lower production cost. One part rather than several is placed on the board, which improves both board build time and reliability.

#### **CONFIGURATIONS**

The AD8273 can be configured in several different ways; see Figure 34 to Figure 41. Because these configurations rely on the internal, matched resistors, these configurations have excellent gain accuracy and gain drift.

#### **POWER SUPPLIES**

A stable dc voltage should be used to power the AD8273. Noise on the supply pins can adversely affect performance. A bypass capacitor of 0.1  $\mu F$  should be placed between each supply pin and ground, as close to each pin as possible. A tantalum capacitor of 10  $\mu F$  should also be used between each supply and ground. It can be farther away from the AD8273 and typically can be shared by other precision integrated circuits.

The AD8273 is specified at  $\pm 15$  V, but it can be used with unbalanced supplies as well, for example,  $-V_S = 0$  V,  $+V_S = 20$  V. The difference between the two supplies must be kept below 36 V.

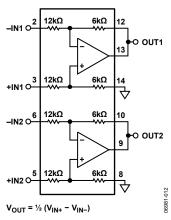

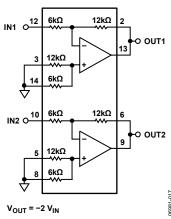

Figure 34. Difference Amplifier,  $G = \frac{1}{2}$

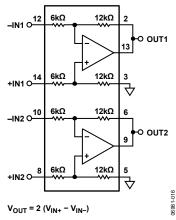

Figure 35. Difference Amplifier, G = 2

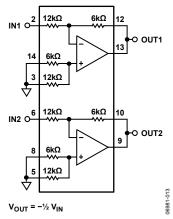

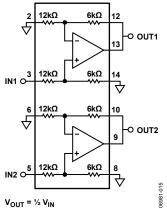

Figure 36. Inverting Amplifier,  $G = \frac{1}{2}$

Figure 37. Inverting Amplifier, G = 2

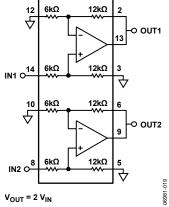

Figure 38. Noninverting Amplifier,  $G = \frac{1}{2}$

Figure 39. Noninverting Amplifier, G = 2

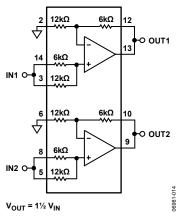

Figure 40. Noninverting Amplifier, G = 1.5

Figure 41. Noninverting Amplifier, G = 3

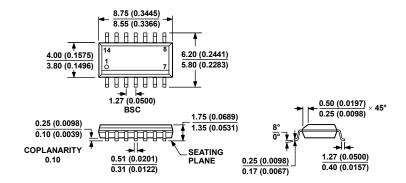

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-012-AB

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 42. 14-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-14) Dimensions shown in millimeters and (inches)

#### **ORDERING GUIDE**

| Model                     | Temperature Range | Package Description               | Package Option |

|---------------------------|-------------------|-----------------------------------|----------------|

| AD8273ARZ <sup>1</sup>    | −40°C to +85°C    | 14-Lead SOIC_N                    | R-14           |

| AD8273ARZ-R7 <sup>1</sup> | −40°C to +85°C    | 14-Lead SOIC_N, 7" Tape and Reel  | R-14           |

| AD8273ARZ-RL <sup>1</sup> | -40°C to +85°C    | 14-Lead SOIC_N, 13" Tape and Reel | R-14           |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

**AD8273**

**NOTES**

**AD8273**

# **NOTES**

| AD8273 |  |  |  |  |

|--------|--|--|--|--|

|--------|--|--|--|--|

NOTES